http://open.bu.edu

Boston University Theses & Dissertations

Boston University Theses & Dissertations

2023

## FPGA-based range-limited molecular dynamics acceleration

https://hdl.handle.net/2144/46688

Downloaded from DSpace Repository, DSpace Institution's institutional repository

### BOSTON UNIVERSITY COLLEGE OF ENGINEERING

#### Dissertation

## FPGA-BASED RANGE-LIMITED MOLECULAR DYNAMICS ACCELERATION

by

#### **CHUNSHU WU**

B.S., Dalian University of Technology, 2016 M.S., Brown University, 2018

Submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

2023

# © 2023 by CHUNSHU WU All rights reserved except for chapter 4, which is ©2021 by IEEE, chapter 5, which is ©2020 by IEEE, chapter 6, which is ©2022 by ACM, chapter 7, which is ©2023 by ACM

#### Approved by

First Reader

Martin C. Herbordt, Ph.D.

Professor of Electrical and Computer Engineering

Second Reader

Richard C. Brower, Ph.D.

Professor of Electrical and Computer Engineering

Third Reader

Tali Moreshet, Ph.D.

Senior Lecturer and Research Assistant Professor of Electrical and Computer Engineering

Fourth Reader

Tong Geng, Ph.D.

Assistant Professor of Electrical and Computer Engineering and Computer Science

University of Rochester

Everybody is a genius. But if you judge a fish by its ability to climb a tree, it will live its whole life believing that it is stupid. Albert Einstein

#### Acknowledgments

I would like to express my deepest gratitude to all those who have supported and guided me throughout my journey in completing this Ph.D. thesis. Their contributions and encouragement have been invaluable, and I am truly grateful for their unwavering support.

First and foremost, I am indebted to my supervisor, Prof. Martin C. Herbordt, for his guidance, expertise, and patience. His insightful feedback, constant motivation, and unwavering belief in my abilities have been instrumental in shaping this research work. I am immensely grateful for his mentorship and for challenging me to reach new heights.

I extend my heartfelt appreciation to the members of my thesis committee, Prof. Richard C. Brower, Prof. Tali Moreshet, and Prof. Tong Geng, for their valuable insights, constructive criticism, and suggestions. Their expertise in their respective fields has immensely enriched this work and broadened my horizons.

I would like to express my special thanks to Prof. Tong Geng at University of Rochester and his family. Their substantial support in both research and life means a lot to me, especially in my early PhD career when I had little knowledge of high performance computing.

I am grateful to Dr. Ang Li at Pacific Northwest National Laboratory, for providing necessary resources and valuable advice to carry out this research. His commitment to excellence and dedication to fostering knowledge have been truly inspiring.

I am indebted to all my colleagues and friends, both within and outside our research group. For my current CAAD lab mates, Pouya Haghi, Anqi Guo, Sahan Bandara, Robert Mufano, Reza Sajjadinasab, Hafsah, Shahzad, and Zaid Tahir, thank you all for creating a harmonic and joyful research environment. For those who already graduated, Zihao Yuan, Chen Yang, Tianqi Wang, Anthony Ducimo, and Pierre-François Wolfe, they generously dedicated their time and efforts to help me conduct this research. Their camaraderie and encouragement have made this journey more fulfilling and enjoyable.

I am grateful to my family for their unwavering love, understanding, and constant sup-

port throughout this journey. Their belief in me and their sacrifices have been the driving force behind my accomplishments. To my parents Ying Zhang and Qinghong Wu, I owe my deepest gratitude for instilling in me a love for learning and for always being my pillars of strength.

I would like to take a special moment to express my deepest gratitude and appreciation to my wife, Yuqing Wang. Her patience, sacrifices, and belief in me have been the driving force behind my perseverance. Thank you, my dear wife, this achievement would not have been possible without you.

Lastly, I would like to express my heartfelt gratitude to all the authors, researchers, and scholars whose works have been referenced in this thesis. Their contributions to the field have been instrumental in shaping my research and expanding my knowledge.

To all those who have played a part, big or small, in the completion of this Ph.D. thesis, please accept my heartfelt appreciation and gratitude. Your support has been invaluable, and I am truly honored to have had the opportunity to work with and learn from each and every one of you.

The research that forms the basis of this dissertation has been partially funded by the NSF through Awards CCF-1618303/7960, CCF-1618303, and CCF-1919130; by the NIH through Award R44GM128533; by grants from Microsoft and Red Hat; by Xilinx and by Intel through donated FPGAs, tools, and IP; by the U.S. Department of Energy, Office of Science, Office of Advanced Scientific Computing Research, ComPort: Rigorous Testing Methods to Safeguard Software Porting, under Award Number 78284. The Pacific Northwest National Laboratory is operated by Battelle for the U.S. Department of Energy under Contract DE-AC05-76RL01830.

FPGA-BASED RANGE-LIMITED MOLECULAR DYNAMICS

**ACCELERATION**

**CHUNSHU WU**

Boston University, College of Engineering, 2023

Major Professor: Martin C. Herbordt, PhD

Professor of Electrical and Computer Engineering

ABSTRACT

Molecular Dynamics (MD) is a computer simulation technique that executes iteratively

over discrete, infinitesimal time intervals. It has been a widely utilized application in the

fields of material sciences and computer-aided drug design for many years, serving as a

crucial benchmark in high-performance computing (HPC). Numerous MD packages have

been developed and effectively accelerated using GPUs. However, as the limits of Moore's

Law are reached, the performance of an individual computing node has reached its bottle-

neck, while the performance of multiple nodes is primarily hindered by scalability issues,

particularly when dealing with small datasets.

In this thesis, the acceleration with respect to small datasets is the main focus. With the

recent COVID-19 pandemic, drug discovery has gained significant attention, and Molec-

ular Dynamics (MD) has emerged as a crucial tool in this process. Particularly, in the

critical domain of drug discovery, small simulations involving approximately  $\sim 50$ K parti-

cles are frequently employed. However, it is important to note that small simulations do

not necessarily translate to faster results, as long-term simulations comprising billions of

MD iterations and more are essential in this context.

In addition to dataset size, the problem of interest is further constrained. Referred

vii

to as the most computationally demanding aspect of MD, the evaluation of range-limited (RL) forces not only accounts for 90% of the MD computation workload but also involves irregular mapping patterns of 3-D data onto 2-D processor networks. To emphasize, this thesis centers around the acceleration of RL MD specifically for small datasets.

In order to address the single-node bottleneck and multi-node scaling challenges, the thesis is organized into two progressive stages of investigation. The first stage delves extensively into enhancing single-node efficiency by examining various factors such as workload mapping from 3-D to 2-D, data routing, and data locality. The second stage focuses on studying multi-node scalability, with a particular emphasis on strong scaling, bandwidth demands, and the synchronization mechanisms between nodes.

Through our study, the results show our design on a Xilinx U280 FPGA achieves  $51.72\times$  and  $4.17\times$  speedups with respect to an Intel Xeon Gold 6226R CPU, and a Quadro RTX 8000 GPU. Our research towards strong scaling also demonstrates that 8 Xilinx U280 FPGAs connected to a switch achieves  $4.67\times$  speedup compared to an Nvidia V100 GPU<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>A100 is outperformed by V100 because it runs at lower frequency (1410 MHz vs. 1530 MHz); more GPUs result in even worse performance compared to 1 GPU.

#### **Contents**

| 1 | Intr | oductio | n                                           | 1  |

|---|------|---------|---------------------------------------------|----|

| 2 | Bacl | kground | d                                           | 10 |

|   | 2.1  | The Ph  | nysical Model of Range-Limited Forces       | 10 |

|   |      | 2.1.1   | RL Force Features                           | 10 |

|   |      | 2.1.2   | Force Integration                           | 12 |

|   |      | 2.1.3   | Periodic Boundary Condition                 | 13 |

|   | 2.2  | MD D    | ata Structure                               | 13 |

|   |      | 2.2.1   | Neighbor List vs. Cell List                 | 14 |

|   |      | 2.2.2   | Filtering                                   | 15 |

|   |      | 2.2.3   | Neighbor Data Importing Layout              | 16 |

|   | 2.3  | FPGA    | Background                                  | 17 |

|   |      | 2.3.1   | FPGA Architecture                           | 17 |

|   |      | 2.3.2   | FPGAs in Molecular Dynamics                 | 19 |

|   |      | 2.3.3   | FPGAs in High Performance Computing         | 21 |

| 3 | Higl | n-Level | Methodologies                               | 22 |

|   | 3.1  | Space   | Decomposition                               | 22 |

|   |      | 3.1.1   | Assumptions and Parameter Declaration       | 23 |

|   |      | 3.1.2   | The Model                                   | 24 |

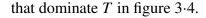

|   |      | 3.1.3   | Quantitative Analysis for the Import Volume | 26 |

|   |      | 3.1.4   | Latency Estimation                          | 27 |

|   | 3.2  | Memo    | ry to PE Mapping Schemes                    | 29 |

|   |      | 3.2.1  | All PEs Work on the Same Reference Particle  | 30 |

|---|------|--------|----------------------------------------------|----|

|   |      | 3.2.2  | All PEs Work on the Same Home Cell           | 32 |

|   |      | 3.2.3  | Each PE Works on a Different Cell            | 33 |

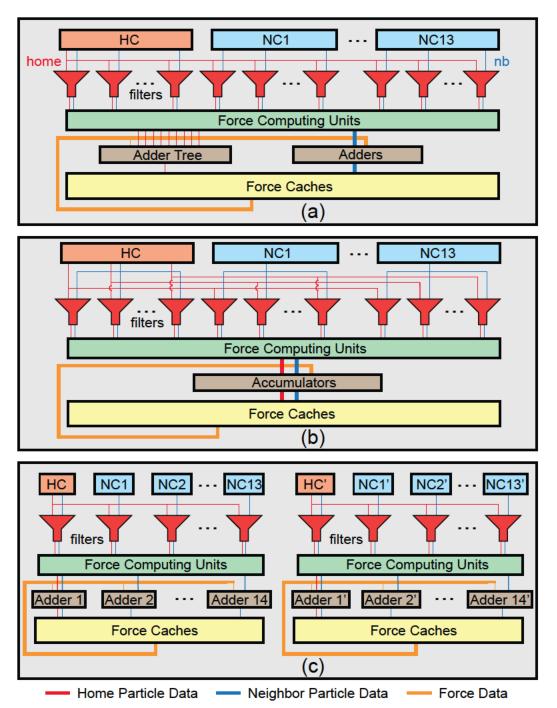

|   | 3.3  | Data F | Format                                       | 34 |

|   |      | 3.3.1  | Position Data Format                         | 34 |

|   |      | 3.3.2  | Force-Related Data Format                    | 37 |

|   | 3.4  | Summ   | ary                                          | 38 |

| 4 | Sing | le-FPG | A Architectures                              | 40 |

|   | 4.1  | Introd | uction                                       | 40 |

|   | 4.2  | Baseli | ne Architectures                             | 42 |

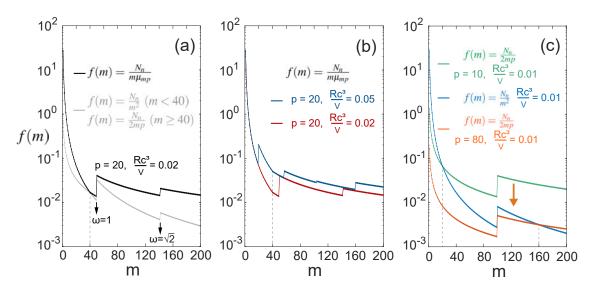

|   |      | 4.2.1  | Design 1: Particle Centric                   | 42 |

|   |      | 4.2.2  | Design 2: Cell Centric                       | 44 |

|   |      | 4.2.3  | Design 3: Uniform Spread                     | 46 |

|   |      | 4.2.4  | Motion Update and Particle Migration         | 48 |

|   | 4.3  | Optim  | ized Designs                                 | 49 |

|   |      | 4.3.1  | Optimized Design 1: Transposed Memory Blocks | 50 |

|   |      | 4.3.2  | Optimized Design 2: On-chip Ring Network     | 54 |

|   |      | 4.3.3  | General Summary of the Optimized Designs     | 66 |

|   | 4.4  | Evalua | ation                                        | 67 |

|   |      | 4.4.1  | Experiment Setup                             | 67 |

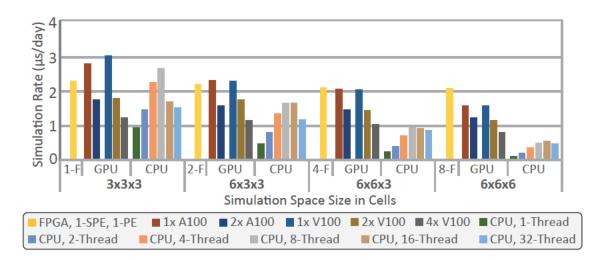

|   |      | 4.4.2  | Performance and Comparison                   | 67 |

|   |      | 4.4.3  | Evaluating Design Options                    | 71 |

|   |      | 4.4.4  | Benchmarking                                 | 73 |

|   |      | 4.4.5  | Hardware Utilization                         | 76 |

|   | 4.5  | Relate | d Work                                       | 76 |

|   | 4.6  | Conclu | asion                                        | 77 |

| 5 | Ban | dwidth | Analysis of FPGAs on a 3-D Torus                         | <b>78</b> |

|---|-----|--------|----------------------------------------------------------|-----------|

|   | 5.1 | Introd | uction                                                   | . 78      |

|   | 5.2 | Multi- | chip baseline design                                     | . 80      |

|   |     | 5.2.1  | Prior-art Single-chip Design                             | . 80      |

|   |     | 5.2.2  | Baseline Multi-chip Design                               | . 80      |

|   |     | 5.2.3  | Communication Bottlenecks of Baseline                    | . 82      |

|   | 5.3 | Optim  | ized Multi-chip Design                                   | . 83      |

|   |     | 5.3.1  | Neighbor Data Caching                                    | . 84      |

|   |     | 5.3.2  | Routing Configuration                                    | . 86      |

|   |     | 5.3.3  | Motion Update Conflict                                   | . 90      |

|   | 5.4 | Evalua | ation                                                    | . 91      |

|   |     | 5.4.1  | Evaluation of Routing Configuration                      | . 92      |

|   |     | 5.4.2  | Evaluation of Neighbor Data Caching                      | . 94      |

|   |     | 5.4.3  | Overall Performance Evaluation                           | . 95      |

|   | 5.5 | Relate | d Work                                                   | . 96      |

|   | 5.6 | Concl  | usion                                                    | . 96      |

| 6 | Opt | imized | Mappings for Symmetric Force Calculations on FPGAs       | 98        |

|   | 6.1 | Introd | uction                                                   | . 98      |

|   | 6.2 | Design | 1                                                        | . 101     |

|   |     | 6.2.1  | Logical Topology                                         | . 101     |

|   |     | 6.2.2  | Corner Caches and Overlapping Position Caches            | . 103     |

|   |     | 6.2.3  | The Modified Manhattan Method                            | 103       |

|   |     | 6.2.4  | Cell Cache Partitioning and Corner Particle Pre-checking | . 104     |

|   |     | 6.2.5  | Architecture                                             | . 105     |

|   |     | 6.2.6  | Memory Misalignment                                      | . 108     |

|   |     | 627    | Multi chin Salution                                      | 100       |

|   | 6.3 | Evalua  | ation                                                       | . 110 |

|---|-----|---------|-------------------------------------------------------------|-------|

|   |     | 6.3.1   | Performance                                                 | . 111 |

|   |     | 6.3.2   | Filtering Rates                                             | . 112 |

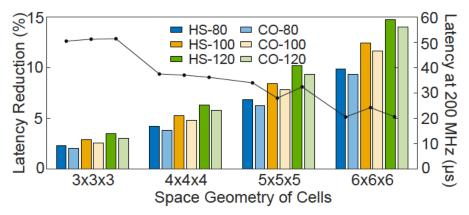

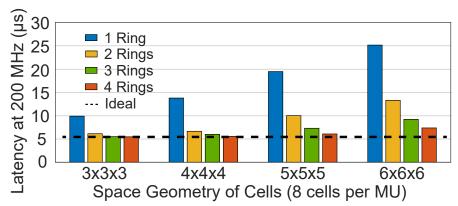

|   |     | 6.3.3   | Position Input Ring Latency                                 | . 112 |

|   |     | 6.3.4   | Motion Update Ring Latency                                  | . 113 |

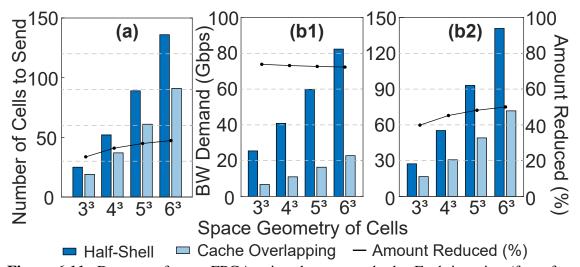

|   |     | 6.3.5   | Multi-FPGA Data Transfer                                    | . 114 |

|   |     | 6.3.6   | Hardware Resource Usage                                     | . 116 |

|   | 6.4 | Relate  | d Work                                                      | . 116 |

|   | 6.5 | Conclu  | usion                                                       | . 117 |

| 7 | FAS | DA: Aı  | n FPGA-Aided, Scalable and Distributed Accelerator for Rang | ge-   |

|   | Lim | ited Mo | olecular Dynamics                                           | 118   |

|   | 7.1 | Introdu | uction                                                      | . 118 |

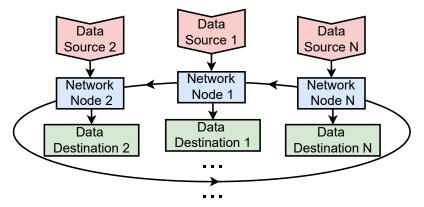

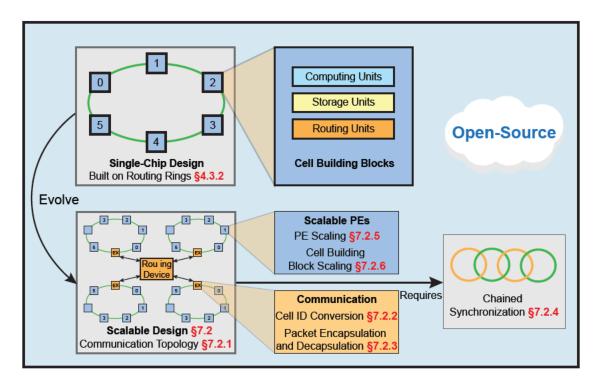

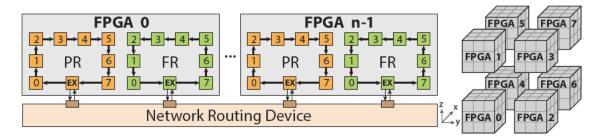

|   | 7.2 | Scalab  | le Architecture                                             | . 122 |

|   |     | 7.2.1   | Hyperring-like Communication Topology                       | . 122 |

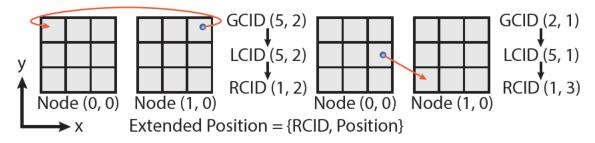

|   |     | 7.2.2   | Cell ID Conversion                                          | . 124 |

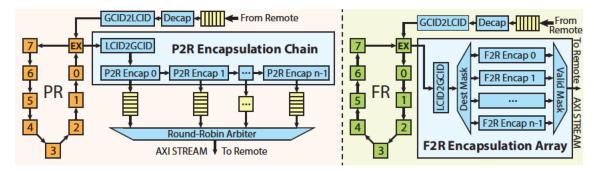

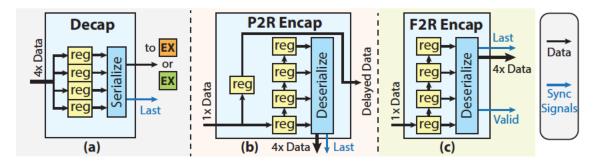

|   |     | 7.2.3   | Communication Interface                                     | . 125 |

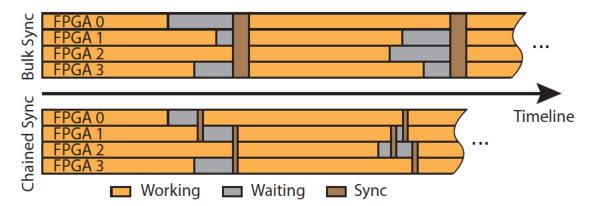

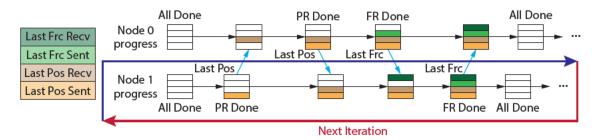

|   |     | 7.2.4   | Chained Synchronization                                     | . 126 |

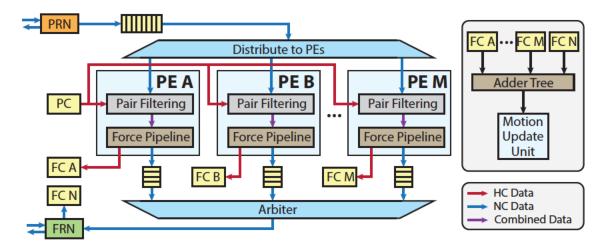

|   |     | 7.2.5   | PE Scaling                                                  | . 128 |

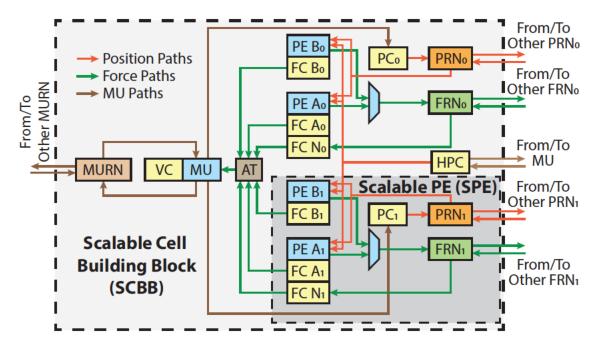

|   |     | 7.2.6   | CBB Scaling                                                 | . 130 |

|   | 7.3 | Evalua  | ation                                                       | . 132 |

|   |     | 7.3.1   | Experimental Setup                                          | . 132 |

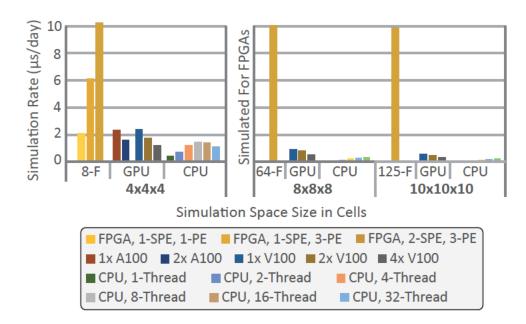

|   |     | 7.3.2   | Overall Performance                                         | . 132 |

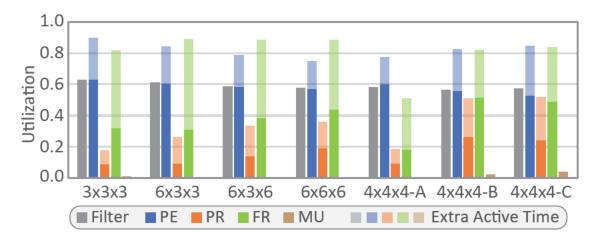

|   |     | 7.3.3   | Utilization Breakdown                                       | . 135 |

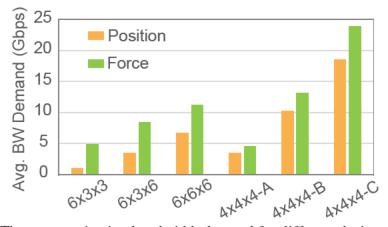

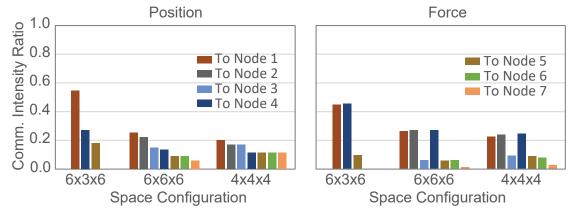

|   |     | 7.3.4   | Communication Intensity                                     | . 136 |

|   |     | 7.3.5   | Resources Consumption                                       | . 138 |

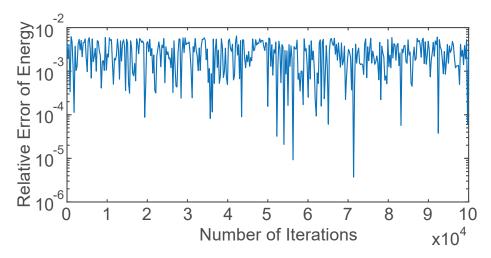

|   |     | 736     | Energy Conservation                                         | 139   |

| Cı | References Curriculum Vitae |                          |     |

|----|-----------------------------|--------------------------|-----|

| Re |                             |                          |     |

|    | 8.2                         | Future Work              | 143 |

|    | 8.1                         | Conclusions              | 142 |

| 8  | Con                         | clusions and Future Work | 142 |

|    | 7.5                         | Conclusion               | 140 |

|    | 7.4                         | Related Work             | 139 |

#### **List of Tables**

| 4.1 | FPGA-O2 performance compared to FPGA-O1, GPU, and CPU with up to                |     |

|-----|---------------------------------------------------------------------------------|-----|

|     | 32 threads                                                                      | 74  |

| 4.2 | FPGA-O2 performance of large simulation spaces compared to FPGA-O1,             |     |

|     | GPU, and 32-thread CPU                                                          | 75  |

| 4.3 | Hardware Utilization of FPGA-O2 with spatial configurations                     | 76  |

| 5.1 | Bandwidth Demand - Pillar (Unit: $w_d f$ )                                      | 87  |

| 5.2 | Bandwidth Demand - Block (Unit: $w_d f$ )                                       | 88  |

| 5.3 | Throughput of a $2\times2\times2$ FPGA cluster. The design runs at 350 MHz fre- |     |

|     | quency, with 50 particles in each cell. Particle: Liquid Argon. Cutoff          |     |

|     | radius: 8.5 Å. Number of ports: 6. Bandwidth of each port: 100 Gbps.            |     |

|     | Data size per packet: 120 bits                                                  | 94  |

| 6.1 | Hardware Costs                                                                  | 116 |

| 7.1 | Hardware Utilization of All Design Variations                                   | 138 |

#### **List of Figures**

| 2.1 | Fundamentals of $R_c$ and the cell list method. (a) The cutoff regions of four         |    |

|-----|----------------------------------------------------------------------------------------|----|

|     | particles. Only A and B interact with each other. (b) A simulation space               |    |

|     | divided into $3\times4\times4$ cells with side length the same as $R_c$ . (c) The home |    |

|     | cell of particle A and 26 adjacent cells unfolded from (b). The green cells            |    |

|     | are regarded as neighbor cells.                                                        | 11 |

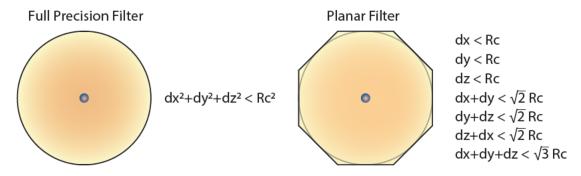

| 2.2 | The 2-D illustration of two filtering methods and the criterion                        | 16 |

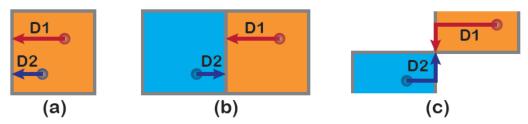

| 2.3 | The mechanism of the traditional Manhattan method shown in 2-D. The                    |    |

|     | particle pairs are evaluated by the processor located in orange cells for              |    |

|     | 3 particle pair scenarios: (a) both in same cell; (b) in neighboring cells             |    |

|     | sharing a boundary; (c) in neighboring cells sharing a corner                          | 17 |

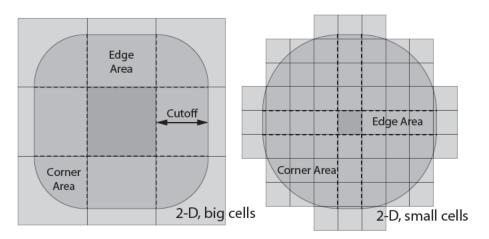

| 3.1 | Neighbor cells in 2-D                                                                  | 25 |

| 3.2 | Import volume in 3-D. A/B/C: face/edge/corner                                          | 25 |

| 3.3 | A variation of Gauss Circle Problem.                                                   | 26 |

| 3.4 | Latency analysis with respect to cell granularity.                                     | 28 |

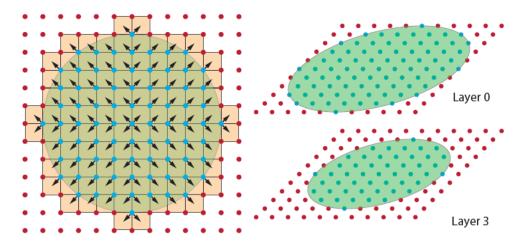

| 3.5 | High level memory-to-PE mapping schemes. (a): particle-centric, all PEs                |    |

|     | work on a single reference particle at a time. (b):cell-centric, all PEs work          |    |

|     | on a same cell at a time. (c): uniformly-spreaded, each PE works on a                  |    |

|     | separate cell.                                                                         | 31 |

| 3.6 | The data format and precision analysis. Top: The fixed-point position for-                 |    |

|-----|--------------------------------------------------------------------------------------------|----|

|     | mat. (a) and (b): Two methods of computing the displacements of particles.                 |    |

|     | (c) and (d): Error analysis of the two methods with different numbers of                   |    |

|     | bits                                                                                       | 36 |

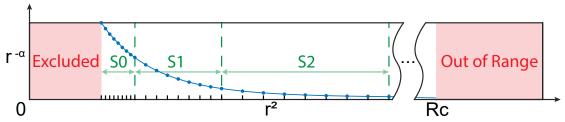

| 3.7 | The interpolation method. $\alpha$ is a positive integer too large for $r^{-\alpha}$ to be |    |

|     | computed. In our case, $\alpha$ is 8 or 14. The small $r$ region is excluded due to        |    |

|     | non-physical high energy                                                                   | 38 |

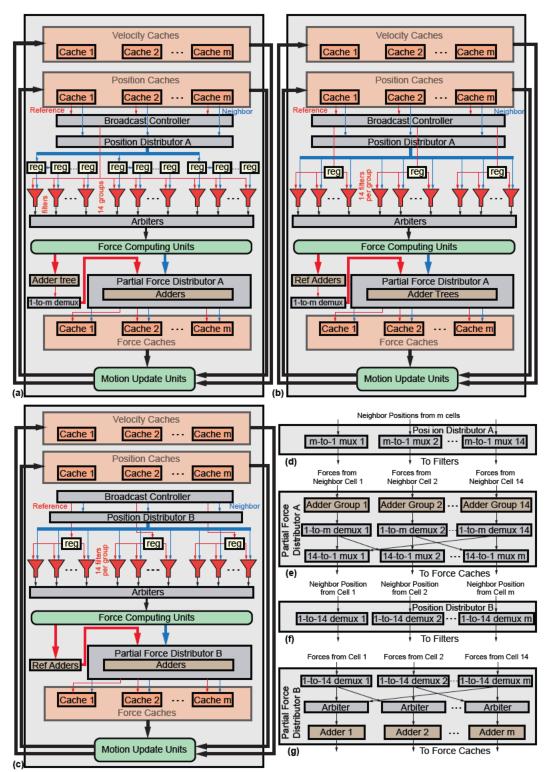

| 4.1 | The baseline designs and detailed distributor architectures. (a)-(c): baseline             |    |

|     | design layouts. (d)-(g): details of position and force distributors                        | 45 |

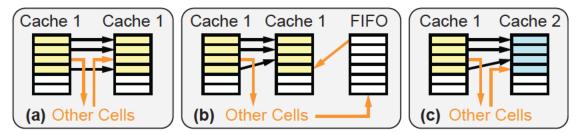

| 4.2 | Particle migration handling methods. (a): directly searching for empty                     |    |

|     | slots. (b): the one-pointer method. (c): double buffering                                  | 49 |

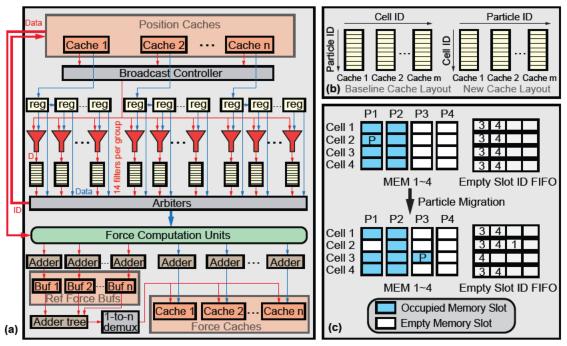

| 4.3 | The optimized architecture for the first mapping scheme. (a): the data                     |    |

|     | flow in force evaluation. For simplicity, arbiters and force computational                 |    |

|     | units are abstracted as entire blocks, and the forces read from force caches               |    |

|     | for accumulation are omitted. (b): the new memory layout compared to                       |    |

|     | baseline. (c): particle migration handling in motion update. P is the particle             |    |

|     | being migrated from cell 2 to cell 3                                                       | 51 |

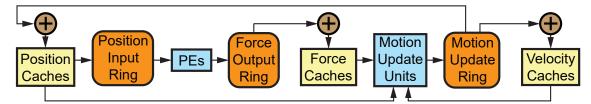

| 4.4 | RL dataflow in brief with rings. Yellow: Memory blocks; orange: Routing                    |    |

|     | rings; blue: computing units                                                               | 55 |

| 4.5 | The ring routing path. Position input ring: from position caches to PEs.                   |    |

|     | Force output ring: from PEs to force caches. Motion update ring: from                      |    |

|     | motion update units to position caches and velocity caches                                 | 55 |

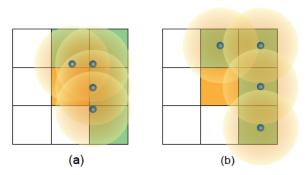

| 4.6 | Example cases of (a) high filter pass rate, (b) low filter pass rate in 2D                 |    |

|     | illustration                                                                               | 58 |

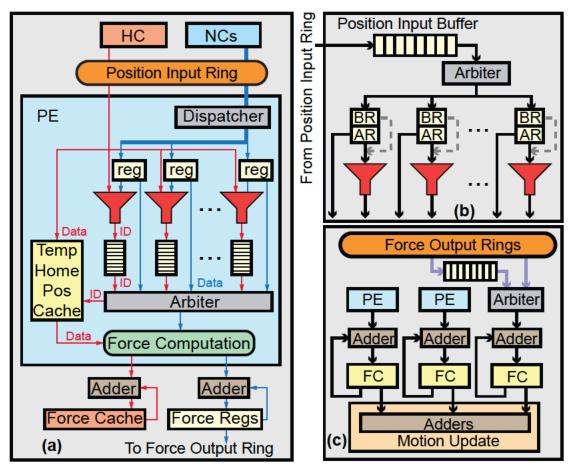

| 4.7  | The optimized design for the third mapping scheme. (a): The data path of          |    |

|------|-----------------------------------------------------------------------------------|----|

|      | a single force computation pipeline. (b): Particle dispatching layout with        |    |

|      | duo registers. AR: Active Register; BR: Backup Register. (c): The partial         |    |

|      | force caches and force aggregation, where the two PEs work on a same              |    |

|      | home cell, and the purple paths are to resolve the conflict when two force        |    |

|      | output rings are used                                                             | 59 |

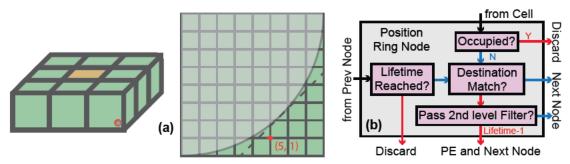

| 4.8  | (a): The 1st level filtering in a position input ring node. Dashed line: planar   |    |

|      | filter criterion. (b): The flowchart of a position input ring node                | 61 |

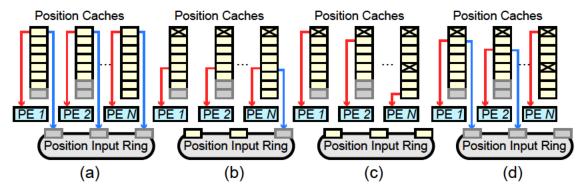

| 4.9  | The out-of-order broadcast method. Gray boxes: Empty slots. Boxes with            |    |

|      | "x": Marked as used. (a) The 1st cycle. (b) The 5th cycle. (c) The 8th            |    |

|      | cycle. (d) the 9th cycle. Red arrows: home particle position; blue arrows:        |    |

|      | neighbor particle position                                                        | 62 |

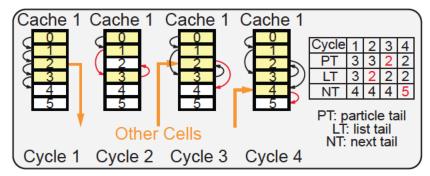

| 4.10 | Particle migration on a linked list with a table showing the pointer values.      |    |

|      | PT points at the last particle, LT points at the last slot of the list, and NT    |    |

|      | points at the next unused slot to be allocated                                    | 63 |

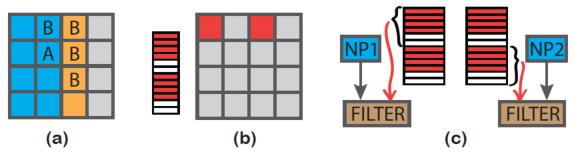

| 4.11 | The solution to the problems emerge in large scale simulations. We intu-          |    |

|      | itively use $4\times4$ 2-D cells with eight PEs for example. (a): blue cells: the |    |

|      | cells currently being processed; orange cells: the extra cells whose data         |    |

|      | are required to process the blue cells. In practice, particles from cell A are    |    |

|      | broadcast to all B cells through a position input ring for particle pairing.      |    |

|      | (b): the memory structure used to achieve higher memory utilization. The          |    |

|      | two red cells are sharing the same memory block at different address do-          |    |

|      | mains. (c): the double buffers are restored to avoid unnecessary memory           |    |

|      | traversal. Two neighbor particles (NP1 and NP2) require data from differ-         |    |

|      | ent cells.                                                                        | 65 |

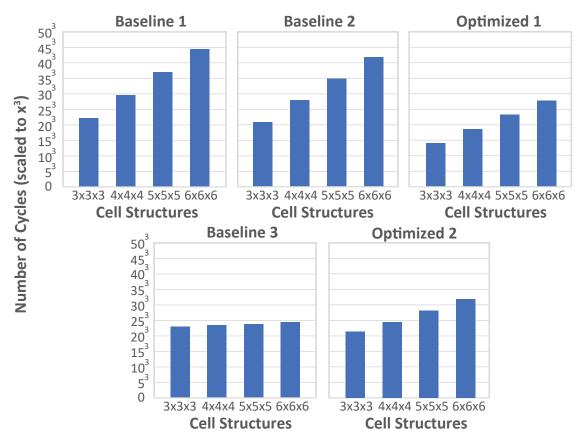

| 4.12 | The performance in cycles per iteration of three baseline and two opti-         |    |

|------|---------------------------------------------------------------------------------|----|

|      | mized designs. We show results for four different cubic cell structures in      |    |

|      | the simulation space to show scalability. The y-axis is scaled to $x^3$ for a   |    |

|      | better illustration of linearity. The dashed line is to split the designs with  |    |

|      | substantial scalability differences                                             | 69 |

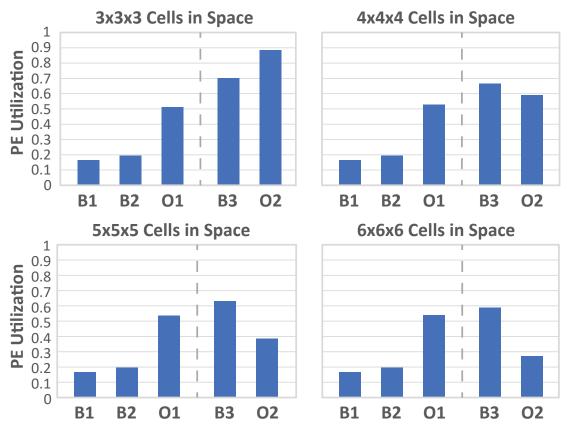

| 4.13 | The PE utilizations of three baseline and two optimized designs. The re-        |    |

|      | sults for four different cubic cell structures in the simulation space are pro- |    |

|      | vided. B1~B3: baseline designs; O1 and O2: optimized designs. The               |    |

|      | dashed lines are used to split the designs with substantial scalability differ- |    |

|      | ences                                                                           | 70 |

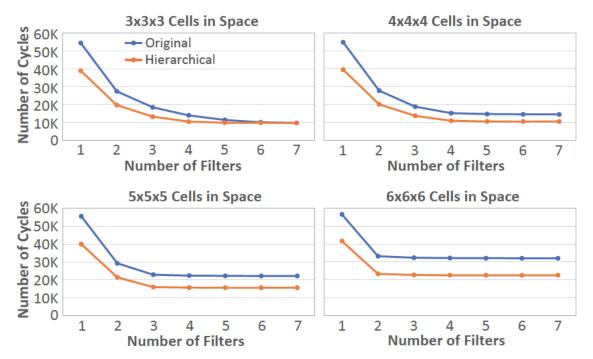

| 4.14 | The performance comparison of the original O2 and O2 with hierarchical          |    |

|      | filters for four representative cell spaces                                     | 73 |

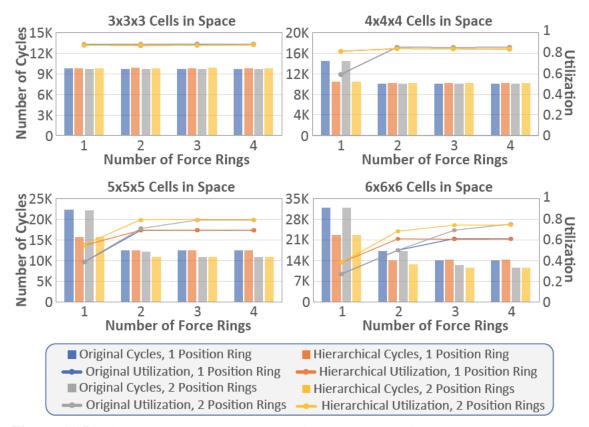

| 4.15 | The performance of the original and hierarchical O2 for four representative     |    |

|      | cell spaces with different numbers of rings equipped                            | 74 |

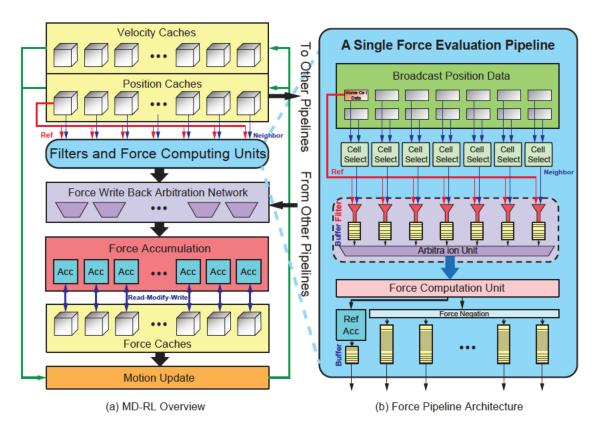

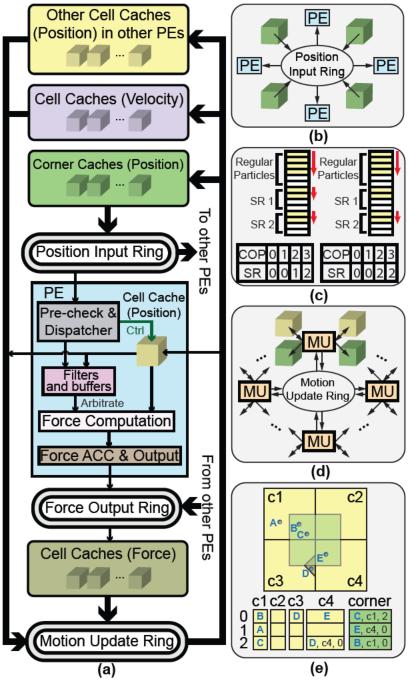

| 5.1  | Architecture of the single-chip design. (a): The general architecture of the    |    |

|      | iterative force evaluation and motion update. (b): Architecture of force        |    |

|      | evaluation pipelines                                                            | 81 |

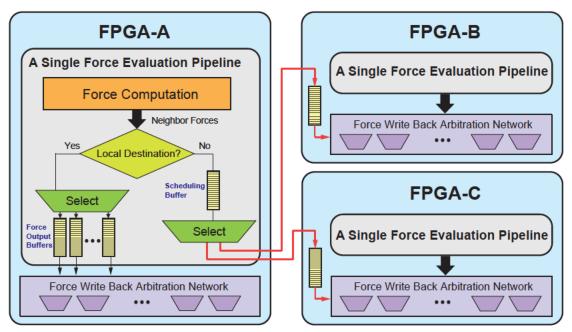

| 5.2  | Force output buffers are re-located to prevent high latency caused by data      |    |

|      | dependency. The scheduling buffer is added in case the bandwidth bottle-        |    |

|      | neck is met                                                                     | 82 |

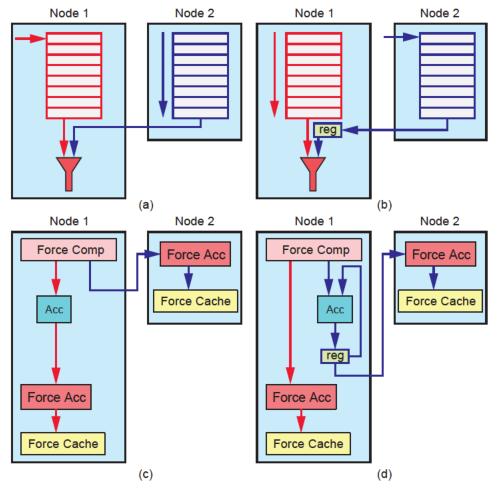

| 5.3  | Position reading and force writing architecture (only 2 position caches in      |    |

|      | 2 nodes are shown for demonstration). (a): Baseline position reading. (b):      |    |

|      | New position reading. (c): Baseline force writing. (d): New force writing.      |    |

|      | Red arrows: Reference data paths. Blue arrows: Neighbor data paths              | 85 |

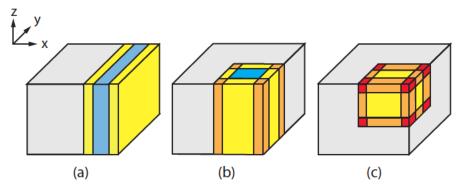

| 5.4 | Workload distribution patterns in a cuboid simulation space. Grey: The         |    |

|-----|--------------------------------------------------------------------------------|----|

|     | cells evaluated on other nodes. Blue: Cells in which particle pairs are        |    |

|     | formed without external memory involved. Yellow: Cells in which data           |    |

|     | from a neighboring FPGA are needed or delivered (1 hop). Orange: 2             |    |

|     | hops. Red: 3 hops. (a): Slab distribution. (b): Pillar. (c): Block             | 87 |

| 5.5 | Reconfigurable force data forwarding pattern examples for the pillar dis-      |    |

|     | tribution. Yellow and orange arrows represent the 1st hop and 2nd hop,         |    |

|     | separately. Blue node: Home FPGA node. Grey node: Neighbor FPGA                |    |

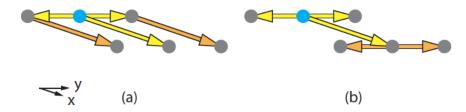

|     | node                                                                           | 88 |

| 5.6 | Reconfigurable force data forwarding pattern examples for the block distri-    |    |

|     | bution. Yellow, orange and red represent the 1st hop, 2nd hop and 3rd hop      |    |

|     | separately. Blue node: Home FPGA node. Grey node: Neighbor FPGA                |    |

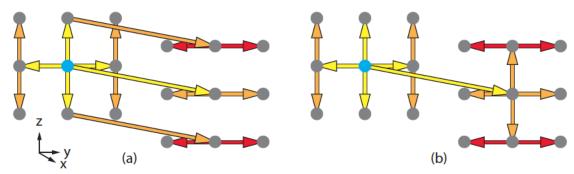

|     | node                                                                           | 89 |

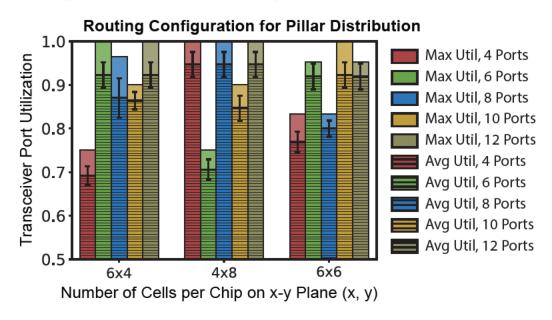

| 5.7 | The port utilization due to the best routing configuration (Max Util) and      |    |

|     | the average utilization (Avg Util) of all routing configurations for 3 typical |    |

|     | pillar distribution cases. Error bar: Standard deviation                       | 92 |

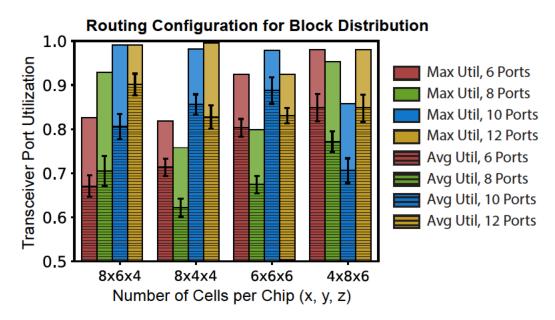

| 5.8 | The port utilization due to the best routing configuration (Max Util) and      |    |

|     | the average utilization (Avg Util) of all routing configurations for 4 typical |    |

|     | block distribution cases Error bar: Standard deviation                         | 93 |

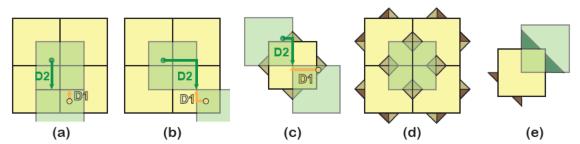

| 6.1 | Cells, spatial partitioning methods, and filtering. $R_c$ : Cutoff radius. (a): |     |

|-----|---------------------------------------------------------------------------------|-----|

|     | the cutoff radius of particles. The force A-B is valid, and A-C and B-C         |     |

|     | forces are too small and neglected. (b): the import volume of the half-shell    |     |

|     | method. (c): the spread layers of (b), where the orange cell at the center      |     |

|     | interacts with 13 blue cells and itself; the middle slice also shows the 2-D    |     |

|     | import volume. (d): 2-D import volume of the Manhattan method. (e):             |     |

|     | planar filtering method. dx and dy are the distance components between          |     |

|     | two particles; particles outside the octagon are not paired with the particle   |     |

|     | at the center.                                                                  | 99  |

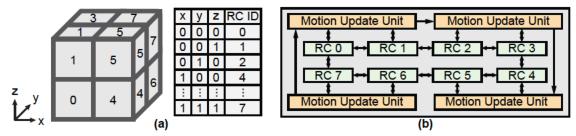

| 6.2 | The overall layout of the design. (a): cell ID numbers are calculated from      |     |

|     | their x, y, and z coordinates in space. (b): the topology of 8 ring cores (RC)  |     |

|     | and 4 motion update units (MUs) for example                                     | 101 |

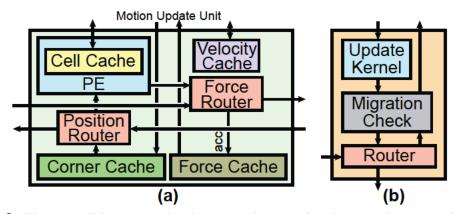

| 6.3 | The overall layout of the design with more details. (a): the internals of a     |     |

|     | ring core. (b): the internals of a MU                                           | 101 |

| 6.4 | The rules of position cache overlapping and the modified Manhattan              |     |

|     | method in 2-D. Yellow cells: cell caches. Green: corner caches. The yel-        |     |

|     | low/green particles are cell particles/corner particles separately, where the   |     |

|     | yellow particles are outlined in black. (a) and (b): the pair is evaluated if   |     |

|     | the neighbor particle has greater Manhattan distance. (c): the brown SRs        |     |

|     | should be included a yellow cache, otherwise the two particles shown will       |     |

|     | never be paired. (d): SR overview. Dark brown: the SRs potentially need         |     |

|     | to be accessed by green particles. (e): Only the green particles in the dark    |     |

|     | green region can may be paired with the SPs in the yellow cell                  | 105 |

| 6.5 | The complete design with the Manhattan method. (a): the data flow with                                                       |

|-----|------------------------------------------------------------------------------------------------------------------------------|

|     | respect to a single PE. (b): the green particles enter the position input ring                                               |

|     | and are rotated to several destination PEs (c): two SR handling cases. Red                                                   |

|     | arrow: data traversal order; left: all SRs are requested; right: SR 1 is not                                                 |

|     | requested and is skipped. COP: corner particle. (d): the motion update                                                       |

|     | ring. Each MU on the ring directly updates several yellow/green caches.                                                      |

|     | (e): corner BRAMs store particle positions, cell IDs and the particle IDs                                                    |

|     | for force write back and memory misalignment handling. The same mech-                                                        |

|     | anism is applied on SPs                                                                                                      |

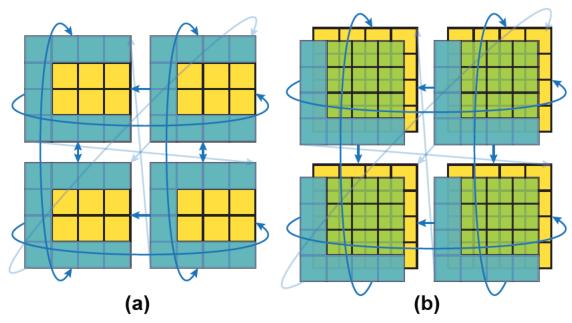

| 6.6 | 2-D illustration of the data transfer pattern for 4 FPGA nodes. (a): half-                                                   |

|     | shell method; (b): the proposed position cache overlapping Manhattan                                                         |

|     | method. Yellow: cell region (SR omitted); Blue: data to be transferred;                                                      |

|     | Green: corner region. The arrows indicate the transfer directions of the                                                     |

|     | position data. For small data transfers at corners, the arrows are lightened 110                                             |

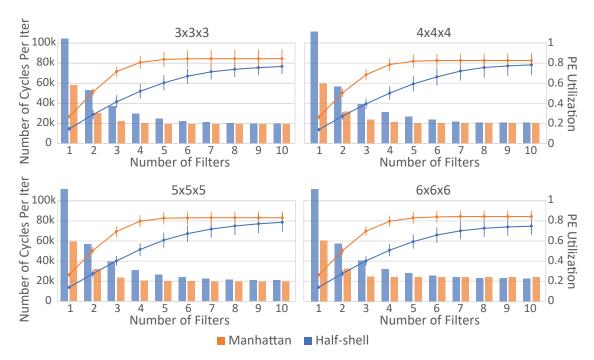

| 6.7 | The performance and PE utilization versus the number of filters for 4 cell                                                   |

|     | geometries. 3 motion update rings and 3 force rings are used. For consis-                                                    |

|     | tency, we assume each cell is processed by 1 PE, and all 4 cases share the                                                   |

|     | same y-axis. Bar: cycle. Curve: utilization                                                                                  |

| 6.8 | Filtering rate and the number of cycles required for filtering for the two                                                   |

|     | methods. For 3 <sup>3</sup> , 4 <sup>3</sup> , 5 <sup>3</sup> and 6 <sup>3</sup> cell geometries, the filtering rates remain |

|     | the same. We assume each cell is only processed by 1 PE for consistency                                                      |

|     | against the scaling of the simulation space                                                                                  |

| 6.9 | The latency of the position input ring of a single MD iteration. HS: half-                                                   |

|     | shell; CO: cache overlapping. 80, 100, 120: number of particles per cell.                                                    |

|     | The line plot indicates the percentage of latency reduced using the cache                                                    |

|     | overlapping method                                                                                                           |

| 6.10 | MU ring latency compared with ideal. Each MU is in charge of updating 8         |     |

|------|---------------------------------------------------------------------------------|-----|

|      | yellow caches and 8 green caches. A cell contains 80 particles                  | 114 |

| 6.11 | Data transfer per FPGA using the two methods. Each iteration (from force        |     |

|      | evaluation to the next force evaluation phase) takes 100 $\mu$ s, with 120 bits |     |

|      | per packet and 80 particles per cell. (a): the number of cells to be sent to    |     |

|      | remote FPGAs. (b1): the estimated ideal bandwidth demand per FPGA for           |     |

|      | a 3-D torus FPGA cluster. (b2): the estimated ideal bandwidth demand per        |     |

|      | FPGA for 8 FPGAs connected as a ring                                            | 115 |

| 7.1  | Overview of FASDA                                                               | 120 |

| 7.2  | The topology of inter-node connection and an example of cell-to-FPGA            |     |

|      | mapping                                                                         | 124 |

| 7.3  | Two levels of cell ID conversion with examples                                  | 124 |

| 7.4  | Arriving/departing data processing. P2R/F2R: position/force to remote           | 125 |

| 7.5  | Details of data processing sub-modules                                          | 125 |

| 7.6  | Two synchronization methods for 4 FPGAs. In this example, each FPGA             |     |

|      | only communicates with its neighbors.                                           | 127 |

| 7.7  | The behavior of the chained synchronization between two FPGA nodes as           |     |

|      | an example. Frc: force. Pos: position                                           | 128 |

| 7.8  | The architecture of a CBB with multiple PEs                                     | 129 |

| 7.9  | The architecture of an SCBB with 2 SPEs, where an SPE consists of 2 PEs         |     |

|      | for example. AT: Adder Tree. HPC: Home Position Cache                           | 130 |

| 7.10 | The weak scalability comparison. 1-F: $1 \times$ FPGA board. 1-SPE: Each        |     |

|      | SCBB contains 1× SPE. 1-PE: Each SPE contains 1 PE                              | 133 |

| 7.11 | The strong scalability comparison. 1-F: $1 \times$ FPGA board. 1-SPE: Each      |     |

|      | SCRR contains 1 × SPE 1-PE: Each SPE contains 1 PE                              | 134 |

| 7.12 | The utilization of key components for the design varieties. A: 1-SPE, 1-PE. |

|------|-----------------------------------------------------------------------------|

|      | B: 1-SPE, 3-PE. C: 2-SPE, 3-PE                                              |

| 7.13 | The communication bandwidth demand for different design configurations. 13  |

| 7.14 | The communication bandwidth demand breakdown for different design           |

|      | configurations                                                              |

| 7.15 | Energy Relative error with respect to OpenMM                                |

#### **List of Abbreviations**

. . . . . . . . . . . . .

. . . . . . . . . . . . .

**GNN**

ACC . . . . . . . . . . . . . Accumulation operation ADD Addition operation . . . . . . . . . . . . . . ALM Adaptive Logic Module on Intel FPGAs . . . . . . . . . . . . . Application-Specific Integrated Circuit **ASIC** . . . . . . . . . . . . . AT Adder Tree . . . . . . . . . . . . . BRAM **Block Random Access Memory** . . . . . . . . . . . . . **BSP** . . . . . . . . . . . . . **Bulk Synchronization Parallel BUF** Buffer . . . . . . . . . . . . . CBB Cell Building Block . . . . . . . . . . . . . **CNN** . . . . . . . . . . . . . . Convolution Neural Network **CONV** . . . . . . . . . . . . . Convolution layer Commercial Off the Shelf COTS . . . . . . . . . . . . . Central Processing Unit CPU . . . . . . . . . . . . . F2R . . . . . . . . . . . . . Force to Ring Force Cache FC . . . . . . . . . . . . . **FCU** Force Computation Units . . . . . . . . . . . . . FF . . . . . . . . . . . . . Flip-Flop First In, First Out **FIFO** . . . . . . . . . . . . . **FLOPS** . . . . . . . . . . . . . Floating Point Operations Per Second **FMC** FPGA Mezzanine Card . . . . . . . . . . . . . FP Floating-Point . . . . . . . . . . . . . **FPGA** Field-Programmable Gate Array . . . . . . . . . . . . . FR Force Ring . . . . . . . . . . . . . **FRN** Force Ring Node . . . . . . . . . . . . . Generative Adversarial Networks GAN . . . . . . . . . . . . . **GCID** . . . . . . . . . . . . . Global Cell ID **GCN Graph Convolutional Network**

Graph Neural Network

| GPU  | <br>Graphics Processing Unit                         |

|------|------------------------------------------------------|

| HBM  | <br>High Bandwidth Memory                            |

| HDL  | <br>Hardware Description Language                    |

| HPC  | <br>High-Performance Computing / Home Position Cache |

| HW   | <br>Hardware                                         |

| LCID | <br>Local Cell ID                                    |

| LR   | <br>Long Range                                       |

| LUT  | <br>Look Up Table                                    |

| MD   | <br>Molecular Dynamics                               |

| ML   | <br>Machine Learning                                 |

| MU   | <br>Motion Update                                    |

| MUR  | <br>Motion Update Ring                               |

| MURN | <br>Motion Update Ring Node                          |

| N3L  | <br>Newton's 3rd Law                                 |

| NN   | <br>Neural Network                                   |

| P2R  | <br>Position to Ring                                 |

| PC   | <br>Position Cache                                   |

| PE   | <br>Processing Element                               |

| PR   | <br>Position Ring                                    |

| PRN  | <br>Position Ring Node                               |

| RAW  | <br>Read After Write                                 |

| RCID | <br>Relative Cell ID                                 |

| REG  | <br>Register                                         |

| RL   | <br>Range Limited                                    |

| RNN  | <br>Recurrent Neural Network                         |

| RTL  | <br>Register Transfer Language                       |

| SCBB | <br>Scalable Cell Building Block                     |

| SoC  | <br>System on Chip                                   |

| SPE  | <br>Scalable PE                                      |

|      |                                                      |

Subtraction operation

Ultra RAM

Velocity Cache . . . . . . . . . . . . . . . .

VAE Variational Autoencoder . . . . . . . . . . . . . . . .

VC

. . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . .

SUB

**URAM**

#### **Chapter 1**

#### Introduction

Molecular Dynamics (MD) is a computational technique that employs physical laws to simulate atomic movements and interactions. Its use is widespread throughout science and engineering. The field of drug discovery has gained significant attention, particularly in light of the COVID-19 pandemic, and MD has emerged as a vital tool for predicting drug-target interactions and optimizing drug properties [Ganesan et al., 2017, Zhao and Caflisch, 2015, Salo-Ahen et al., 2020, Liu et al., 2018]. However, the process of discovering new drugs is typically time-consuming and expensive, requiring substantial investments and years of work [Mullard, 2014]. To mitigate these challenges, accelerating the drug discovery process through MD simulations, especially for small particle sets (~50K), is crucial [Mortier et al., 2015, Aminpour et al., 2019, Salo-Ahen et al., 2020].

Despite the small dataset size, the execution of MD simulations is not necessarily simple. To ensure accuracy, MD simulations iterate over discrete time intervals, often on the order of femtoseconds ( $10^{-15}$  seconds), resulting in billions of iterations for *long timescales* ( $10^{-6}$  and beyond). However, due to data dependencies, parallelizing sequential iterations poses a significant challenge, particularly for achieving strong scaling and accelerating limited workloads within a single iteration. Consequently, an approach that can maintain high efficiency with numerous powerful computing nodes, each handling a small portion of data, is necessary.

While there are several MD software packages available [Case et al., 2005, Phillips et al., 2005, Eastman and Pande, 2010, Abraham et al., 2015, Thompson et al., 2022, Bowers

et al., 2006a], some of which support both CPUs and GPUs, CPUs generally exhibit lower computational capabilities, resulting in lower performance compared to GPUs.

The real difficulty, however, is strong scaling: i.e., scaling performance (length of time simulated per wall-clock time) while keeping the problem size constant. As the time simulated per day increases into the microseconds and beyond, the wall-clock time per iteration reduces through milliseconds down to 100s of microseconds and beyond. The (well-known) challenge of strong scaling is that more nodes are required to more quickly perform the computations, but these additional increase the complexity of the communication. Communication eventually dominates: it clearly makes no sense to simulate a few thousand particles with a similar number of nodes. Any solution requires:

- 1. Maximally powerful nodes,

- 2. Minimum internode communication latency, and

- 3. Minimal overhead in interaction between computation and communication.

Their widespread availability, and (comparative) ease of use, makes GPUs the technology of choice for *throughput* and *weak scaling* scenarios [Páll et al., 2020, Glaser et al., 2015]. A typical *throughput* scenario is the testing of a large number of small molecules, say, drug candidates, for a limited timescale, say, for a few hundred nanoseconds. In *weak scaling* scenarios the problem size is large, say, many millions of particles, and computation remains dominant over communication. In the *throughput* scenario, an economical computational alternative is a generic cluster with node-attached GPU accelerators. These resources can also be accessed in commercial clouds such as AWS. In the *weak scaling* scenario, a more powerful communication network is likely to be needed, but one that is typically provided in a High Performance Computing (HPC) cluster.

However, in *strong scaling* scenarios, the second and third parts of the solution must be upgraded. For small simulations GPUs configurations have so far failed to scale beyond one to two processors. In fact the problem is regarded as being so difficult that the only successful alternative (prior to this work) is created a fully custom supercomputer including the building of Application Specific Integrated Circuits (ASICs). These systems are remarkable achievements, offering exceptional performance exactly because they satisfy all three conditions. For instance, Anton 3 can attain a simulation rate of  $\sim 200 \, \mu s$ -per-day for 10K particles with 512 nodes [Shaw et al., 2021]. Meanwhile, its predecessor, Anton 2, can achieve around 100  $\mu s$ -per-day with the same number of nodes [Shaw et al., 2014]. However, their high cost, limited accessibility, and maintenance and upgrade issues hinder their widespread adoption, thus offering limited contribution to the community.

The focus of this dissertation is FPGAs. Similar to ASICs, FPGAs provide hardware flexibility without the same availability and maintenance concerns. Additionally, FPGAs possess low-latency communication capabilities, making them well-suited for MD applications that involve frequent data exchange between multiple FPGA nodes. We note that this low-latency is two parts. First, FPGAs are built so that they can be interconnects pin-to-pin in low latency clusters with point-to-point latency of 100ns or less. And second, within the FPGA the computation and communication logic can be integrated seamlessly so that only a few cycles are needed to get from the application to the communication interface. This combination of flexibility, low latency, and competitive computing power makes FP-GAs an ideal choice for achieving strong scaling with commercial off-the-shelf (COTS) components.

FPGAs have also evolved significantly over the years, with on-chip resources increasing from hundreds to nearly a million logic blocks, enabling researchers and engineers to program them for complex applications such as MD with high performance. Recent FPGA-based MD studies have also demonstrated superior performance to GPUs of similar generations, even on a single node [Yuan et al., 2022, Yang et al., 2019a, Wu et al., 2021b].

In MD simulations, a significant portion of the computation revolves around the eval-

uation of non-bonded forces, which can be divided into two components: N-body range-limited (RL) forces with a cutoff and long-range (LR) force evaluation. RL forces constitute the majority (approximately 90%) of the computation and are highly compute-intensive, while LR forces are more focused on memory and communication aspects. These two components can be treated as separate tasks due to their relatively independent data flow. This thesis primarily focuses on the RL component, which has been the main subject of initial studies on FPGA-based MD simulations [Azizi et al., 2004, Hamada and Nakasato, 2005, Gu et al., 2005a, Kindratenko and Pointer, 2006, Scrofano et al., 2008]. Specifically, computation, communication, and memory access of RL are all studied in depth.

Having identified the operating platform and the specific problem at hand, our focus shifts towards achieving strong scaling in Molecular Dynamics (MD). To fulfill our goal, we must address two primary challenges in a sequential manner. Firstly, we need to determine how to **maximize the potential of a single FPGA**, ensuring high efficiency in MD computations. Subsequently, we must tackle the task of **constructing a multi-FPGA system** that not only maintains the efficiency achieved on a single FPGA but also exhibits strong scalability. By approaching these two high-level problems in a progressive order, we can effectively advance towards our objective of achieving both high efficiency and strong scalability in MD simulations.

To tackle the first challenge, an extensive examination is undertaken to thoroughly investigate three high-level 3-D to 2-D workload mapping schemes. These mapping schemes, characterized by different levels of granularity in workload partitioning, offer distinct advantages in various scenarios. Among these schemes, two design variations are proposed, both leveraging data locality while employing distinct data routing mechanisms. Through this comprehensive exploration, we establish the methodologies necessary to attain high efficiency on a single FPGA node.

The second challenge encompasses not only the need for an efficient design at the

single-node level but also demands efficient inter-node communication, synchronization, and strong scaling. In terms of communication, the partitioning of workloads and the interaction patterns among nodes play a crucial role. Thus, we conduct an analysis of the bandwidth requirements and propose a method for balancing the bandwidth specifically tailored for FPGAs. Additionally, recognizing the potential reduction in overall bandwidth requirements through exploiting the force symmetry property, we introduce a modified Manhattan method that significantly reduces data transfer by over 40%.

Addressing synchronization and strong scaling, we propose a completely distributed and decentralized computing system with scalable processing elements (PEs). By eliminating the need for a central authority, we simplify inter-node communication and reduce latency. Furthermore, expanding the system by adding more nodes requires minimal additional effort. To ensure efficient synchronization, we incorporate a localized synchronization mechanism that avoids the overhead associated with global synchronization methods such as Bulk Synchronization Parallel (BSP). This localized approach effectively maintains a fully distributed system, enabling optimal performance and scalability.

The establishment of the system owes much to the emergence of FPGAs in cloud computing. Prominent cloud platforms such as Microsoft Azure [Zhang et al., 2017], Amazon EC2 F1 [ama, ], FAbRIC [uta, ], Chameleon Cloud [Keahey et al., 2020], and Open Cloud Testbed [Handagala et al., 2022] now provide accessible FPGA clusters. These platforms allow for seamless access to FPGA resources, facilitating the deployment of FPGA-based designs. As a result, we anticipate a rising trend in the development of FPGA applications in the near future, driven by the availability and accessibility of FPGA clusters offered by these cloud platforms.

Next, the specific work is listed with more detailed description.

1. Single-FPGA Design 1: Transposed Memory Blocks. This design stems from the finest-grained among the three 3-D to 2-D workload mapping schemes, where all PEs pro-

cess the same particle at the same time. In conventional approaches, particles within a region are grouped together and stored sequentially in a memory block. However, in this design, the particles within a group are distributed across different memory blocks, enabling parallel access. As a result, concurrent processing of a single particle becomes possible, enabling high parallelism even for the most fine-grained workload mapping scheme.

- 2. Single-FPGA Design 2: Cell-based Workload Partitioning. This design is derived from the coarsest-grained mapping scheme among the three 3-D to 2-D workload mapping schemes. In this scheme, each processing element (PE) is responsible for processing a group of particles within a specific region. While this approach necessitates the incorporation of a daisy chain data routing mechanism to mitigate fan-in and fan-out challenges, it offers remarkable flexibility in parallelism and structured scaling in space. To further enhance efficiency, technologies such as hierarchical filters and out-of-order position broadcast are employed.

- 3. FPGAs on a 3-D torus: Bandwidth analysis and communication balancing. The 3-D torus topology is a commonly employed network structure for 3-D applications, including MD. This topology, utilized in systems like the Anton series, is well-suited for FPGAs, given the availability of sufficient communication ports. In this study, a comprehensive analysis is conducted on three different data partitioning patterns for FPGAs: slabs, pillars, and blocks. However, it is observed that the latter two patterns result in imbalanced communication intensity along different directions, leading to underutilized communication ports. To address this imbalance issue, we propose a static communication balancing mechanism. This mechanism aims to optimize overall communication intensity by effectively redistributing the communication load, leveraging the available bandwidth to its fullest potential. By implementing this approach, we achieve higher overall communication intensity while utilizing the given bandwidth efficiently.

- 4. Multi-FPGA bandwidth demand reduction: The exploration of force symmetry. Deter-

mining the optimal mapping of particles and computations to memories and processors is a complex task when parallelizing the computation of pairwise forces. However, achieving this optimal mapping can lead to significant reductions in data movement and computation. For many years, the exploration of mappings on FPGAs has been relatively limited, with the half-shell method being the preferred approach in prior studies. In this research, we discover that the Manhattan method surprisingly aligns well with FPGA hardware. By introducing the cache overlapping technique, we effectively address the requirement for ultra-fine-grained data access imposed by the Manhattan method, even though the memory blocks on FPGAs may not appear to be fine-grained enough. Eventually, our results show that we achieve balanced communication and significantly reduce data transfer by 40% to 75% in typical multi-FPGA scenarios. This finding is particularly valuable in the cases where communication bandwidth is limited, offering notable benefits in data transfer.

5. FASDA: An FPGA-Aided, Scalable and Distributed Accelerator for Range-Limited Molecular Dynamics. Our research in MD RL is driven by the overarching goal of achieving high efficiency on a single FPGA node while also enabling strong scaling across multiple FPGA nodes. To achieve this, we recognize the significant advantages of employing a completely distributed and decentralized computing system. By eliminating the need for a central authority, our system simplifies inter-node communication, reduces latency, and allows for seamless expansion of the system by adding more nodes with minimal additional effort. In line with these objectives, we introduce FASDA, which, to the best of our knowledge, is the first scalable and fully distributed RL N-body simulation system with a cutoff that leverages the customizable nature and communication efficiency of FPGAs. Moreover, FASDA is designed with a modular structure, enabling the integration of easily pluggable components that can be adjusted based on user requirements and available resources with minimal modifications.

In summary, this dissertation chronicles progress made in accelerating MD RL on FP-

GAs, beginning with the construction of single-node designs based on various 3-D to 2-D mapping schemes, and culminating in a multi-FPGA design that leverages the efficiency achieved in the single-FPGA designs, while enabling strong scaling in the meantime. Along this journey, our research not only accelerates MD RL on FPGAs but also offers valuable insights applicable to other applications that exhibit a localized data interaction pattern. By documenting these advancements, we contribute to the broader understanding of FPGA-based acceleration and its potential in optimizing performance for applications with similar characteristics.

The overall contributions of this dissertation are as follows:

- Problem Definition and Methodology: The objective of our research is to accelerate MD RL through a two-step approach. Firstly, we focus on optimizing the efficiency of single-FPGA designs. Secondly, we expand our efforts to encompass multi-FPGA configurations, aiming to achieve strong scaling.

- New Architectures: Our research has resulted in the development of a set of innovative hardware architectures that effectively enhance performance and minimize bandwidth requirements in communication.

- Performance: Our research successfully demonstrates the efficacy of the proposed methods, showcasing performance improvements of 4 to 5 times when compared to relevant prior art.

- Advancing Computing Technology for MD: In our research, we leverage the emerging FPGA cluster platforms to map and implement our designs. Through our experimentation and analysis, we provide compelling evidence that FPGA clusters are not only competitive but also demonstrate superiority over other computing technologies in terms of high-performance computing and strong scaling.

The subsequent sections of this dissertation are structured as follows. Chapter 2 provides the necessary background information and covers preliminary work in the field. Moving forward, Chapter 3 describes the high-level methodologies including space partitioning and workload mapping. Chapter 4 delves into the details of the single-FPGA designs. The subsequent three chapters focus on multi-FPGA solutions, each addressing a different aspect. Chapter 5 examines bandwidth analysis and communication balancing of FPGAs within a 3-D torus topology. Chapter 6 explores the utilization of force symmetry to reduce the demand for bandwidth. In Chapter 7, we present a scalable and fully distributed MD RL accelerator implemented on an FPGA cluster. Finally, Chapter 8 concludes the dissertation, summarizing the key findings and discussing potential future research directions.

#### **Chapter 2**

#### **Background**

This chapter serves to provide a comprehensive background on MD RL theories and algorithms, as well as the fundamentals of FPGAs. Firstly, we delve into the underlying physical model and algorithm that govern the calculation of forces and their relationship to particle distances. Next, we discuss common physics-based optimizations and the corresponding data structures that arise from them. Lastly, we introduce the architecture of FPGAs and their utilization in accelerating MD RL computations.

#### 2.1 The Physical Model of Range-Limited Forces

This section briefly introduces the MD RL algorithm and the physical principles within.

#### 2.1.1 RL Force Features

The RL forces in MD simulations comprise of two distinct components. Firstly, there is the short-range term of electrostatic force, which is commonly computed using methods such as Particle Mesh Ewald (PME) or similar techniques [Darden et al., 1993]. Secondly, there is the force derived from the Lennard-Jones (LJ) potential, which contributes to the overall RL force calculation. In this work, we refer to RL forces as only the latter to avoid unnecessary LR discussions.

The LJ potential is a mathematical representation of the Van der Waals interaction observed between electrically neutral particles. It describes the potential energy between two particles, labeled as i and j, based on their distance  $r_{ij}$ . The LJ potential equation is ex-

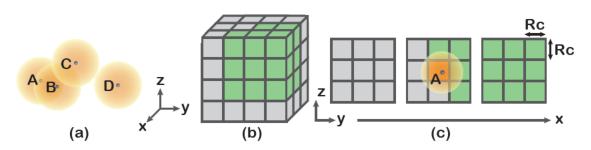

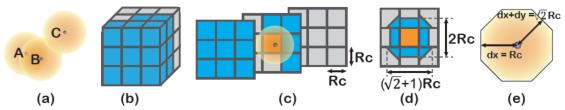

Figure 2.1: Fundamentals of  $R_c$  and the cell list method. (a) The cutoff regions of four particles. Only A and B interact with each other. (b) A simulation space divided into  $3\times4\times4$  cells with side length the same as  $R_c$ . (c) The home cell of particle A and 26 adjacent cells unfolded from (b). The green cells are regarded as neighbor cells.

pressed as follows:

$$V_{ij}^{LJ} = 4\varepsilon_{ij} \left[ \left( \frac{\sigma_{ij}}{r_{ij}} \right)^{12} - \left( \frac{\sigma_{ij}}{r_{ij}} \right)^{6} \right]$$

(2.1)

The potential is influenced by two parameters:  $\varepsilon$ , which represents the dispersion energy and determines the amplitude of the potential, and  $\sigma$ , which represents the characteristic distance between particles where the LJ potential is zero. By taking the gradient of the potential, we can calculate the range-limited (RL) force between particle i and j:

$$\mathbf{F}_{ij}^{LJ} = \frac{\varepsilon_{ij}}{\sigma_{ij}^2} \left[ 48 \left( \frac{\sigma_{ij}}{r_{ij}} \right)^{14} - 24 \left( \frac{\sigma_{ij}}{r_{ij}} \right)^8 \right] \mathbf{r}_{ij}$$

(2.2)

Equation 2.2 reveals that the computational complexity of range-limited (RL) forces in MD RL is  $O(N^2)$  since forces need to be calculated between every pair of particles. However, it can be observed that the force diminishes rapidly as the distance  $r_{ij}$  increases, indicating that the contribution of distant particles to the force is negligible. To address this, a cutoff radius ( $R_c$ ) is introduced. For particle pairs with  $r_{ij} > R_c$ , the force is considered to be zero, allowing us to ignore the computation of pairwise forces beyond this distance. This cutoff radius is visually represented by halos in Figure 2·1(a). For instance, Particle A interacts only with Particle B because A is within B's halo, and vice versa. Particle C and D have minimal impact on the resultant force of A, and thus their contributions

can be disregarded in A's computation. As a result, the overall computational complexity reduces to O(mN), where m represents the average number of neighboring particles for each particle. Typically, m is much smaller than N.

Moreover, the total computation can be effectively reduced by half since the pairwise forces between particles have an equal and opposite effect on each participating particle, in accordance with Newton's third law (N3L).

# 2.1.2 Force Integration

The MD procedure consists of two main phases: force evaluation and motion update, which are iteratively executed. In the force evaluation phase, the pair-wise forces between particles are computed using Equation 2.2 based on their current positions. These forces are then accumulated to determine the resultant force acting on each particle. Once all the forces are computed, the motion update phase begins. The resultant forces are utilized to calculate the changes in velocity and position for each particle, following a specific integration method. In this study, the Verlet Integrator is adopted due to its low hardware cost and favorable numerical stability. The Verlet Integration method with an error of  $O(\Delta t^2)$  is introduced:

$$\mathbf{a}(t) = \frac{\mathbf{F}(t)}{m} \tag{2.3}$$

$$\mathbf{v}(t+\Delta t) = \mathbf{v}(t) + \frac{\mathbf{a}(t) + \mathbf{a}(t+\Delta t)}{2}t$$

(2.4)

$$\mathbf{r}(t + \Delta t) = \mathbf{r}(t) + \mathbf{v}(t + \Delta t)\Delta t \tag{2.5}$$

Compared to force evaluation, motion update is much less computationally intensive as it is applied only once per particle.

# 2.1.3 Periodic Boundary Condition

Periodic boundary conditions are a commonly employed technique in solid-state physics and computational physics when studying large or infinite homogeneous systems. This approach allows for the modeling of a small system that is replicated to represent the entire system. With periodic boundary conditions, particles that exit the small system on one side re-enter from the opposite side with the same velocity, creating a seamless periodicity in the simulation.

By applying periodic boundary conditions, important conservation properties of the system are maintained. The number of particles, denoted by N, remains constant throughout the simulation. The volume of the simulation space, represented by V, also remains unchanged. Additionally, the total energy of the system, denoted by E, is conserved in the absence of external energy input. These conservation properties make the simulation compatible with a microcanonical ensemble (NVE ensemble), as if the system is isolated from its surroundings.

In addition to the conservation of particle number, volume, and energy, periodic boundary conditions allow for the determination of environmental parameters such as temperature. By performing simulations using periodic boundary conditions, it becomes possible to study the thermodynamic behavior of the system and obtain information about its temperature distribution. This is achieved by analyzing the kinetic energies and velocities of particles within the simulation.

#### 2.2 MD Data Structure

In this section, we first compare and analyze two commonly used data structures, and analyze their pros and cons specifically for FPGAs. Second, we discuss a methodology for optimizing memory efficiency on FPGAs by partitioning the simulation space. Finally, we examine the communication patterns between FPGA nodes, particularly focusing on the

import volume associated with different spatial decomposition methods. In our case, only on-chip memory is used to avoid the latency in off-chip data access.

#### 2.2.1 Neighbor List vs. Cell List

Neighbor List. Conventionally, particle data is organized using neighbor lists and cell lists. In the case of neighbor lists, a list of neighboring particles is created for each individual particle in the simulation space. While this approach allows for fast data retrieval when evaluating a particle, it has two main limitations. Firstly, it does not effectively exploit data locality. A particle can appear as a neighbor in multiple neighbor lists with different addresses, resulting in duplicated data and disordered data access. This can consume significant memory capacity and bandwidth, particularly on FPGAs where on-chip memory resources are limited. Secondly, maintaining neighbor lists can be challenging. When a particle moves during an MD iteration, it needs to be removed from certain neighbor lists and added to others. Identifying and updating these neighbor lists can be complex and resource-intensive. Although the neighbor list method may be efficient in scenarios where memory resources are abundant, it may not be ideal for FPGAs where memory can easily become a bottleneck.

Cell List. In practice, the neighbor list method can be replaced by the cell list method with hardware-based filtering in implementations. The cell list approach involves spatially grouping particles before evaluation. As depicted in Figure 2·1(b), the simulation space is divided into cubic cells, such as a  $3\times4\times4$  configuration, with a specific side length denoted as  $R_c$ . Each cell contains a separate memory domain to store the particles assigned to it. For instance, in the case of a  $3\times4\times4$  setup, a total of 48 memory regions are allocated for particle storage, corresponding to each individual cell.

Suppose particle A is located within cell (1, 2, 2). In this scenario, only the particles in the green neighboring cells (including the home cell itself) need to be checked for valid particle pairs with particle A. By applying N3L, only 14 out of the 27 surrounding cells

need to be considered as neighbor cells, as illustrated in Figure  $2 \cdot 1(c)$  using the half-shell method. Additional layouts for importing neighbor data are discussed in section 2.2.3. The cell lists effectively categorize particles in a geometric manner, promoting high data locality. Consequently, a particle can be broadcast to its neighboring cells for pairing. However, it should be noted that only approximately 15% of the neighbor particles are expected to form valid pairs with the reference particle, as indicated by the equation below:

$$P = \frac{\frac{4}{3}\pi R_c^3}{27R_c^3} = 15.5\% \tag{2.6}$$

The denominator in the equation represents the volume of the  $3\times3\times3$  cells surrounding a home cell, which has a side length equal to the cutoff radius  $R_c$ . This justification will be discussed in more detail in section 3.1. The numerator, on the other hand, corresponds to the volume of a sphere with a radius of  $R_c$ . As a result, it is desirable to perform preliminary particle pair filtering, where a force computing unit receives particle pairs from multiple filters to ensure efficient utilization and avoid idleness.

#### 2.2.2 Filtering

In hardware implementations, locality out-weighs resources. That is to say, rather than constructing precise neighbor lists, we leverage the locality introduced by the cell-list method to minimize the number of data transactions per particle at the expense of deploying filters. Fortunately, the filtering process itself requires only a small amount of on-chip resources [Chiu and Herbordt, 2009], particularly when employing planar filtering, which utilizes low-precision integer comparisons.

Figure 2·2 provides an illustration of the two filter mechanisms. The full precision filter involves 3 multiplications and 5 additions, while the planar filter requires only 5 additions. Due to the absence of multiplications, the planar filter can be implemented using, for example, 8-bit fixed-point data, taking advantage of the linearity of the constraints. In

Figure 2-2: The 2-D illustration of two filtering methods and the criterion.

contrast, multiplications incur much higher hardware costs and necessitate more bits for accuracy. Considering the resource consumption, the planar filter mechanism is chosen throughout all our work, as hundreds of, or even a thousand filters are to be deployed, despite introducing 13% more pairs to be filtered.

## 2.2.3 Neighbor Data Importing Layout

The layout for importing neighbor data is fundamentally determined by the interpretation of N3L. One of the viable approaches for handling neighbor data import is the half-shell method (depicted in Figure 2·1(c)). In this method, 14 out of 27 neighbor cells are directly imported for a home cell without any additional cell partitioning. Other methods include the Neutral Territory (NT) method used in Anton 1 and 2 [Bowers et al., 2007, Bowers et al., 2006b], and the Hybrid Manhattan method used in Anton 3 [Shaw et al., 2021]. However, unlike ASICs, FPGAs rely on block RAMs (BRAMs) for data storage. Each BRAM typically has a depth of hundreds of entries and a width of tens of bits, making it suitable for storing data chunks rather than fine-grained data fragments. In comparison to the NT and Manhattan methods, the half-shell method provides easy organization of data by cells and allows for efficient memory access, but at the cost of a higher import volume. In chapter 6, a modified manhattan method will be demonstrated to overcome the problem in fine-grained memory access and reduce the overall import volume.

Figure 2·3: The mechanism of the traditional Manhattan method shown in 2-D. The particle pairs are evaluated by the processor located in orange cells for 3 particle pair scenarios: (a) both in same cell; (b) in neighboring cells sharing a boundary; (c) in neighboring cells sharing a corner.

To address the neighbor data importing problem in a general sense, we need to determine whether to compute the force  $F_{a, b}$  when particle a or particle b is chosen as the reference particle, in order to avoid redundant force calculations. Figure 2·3 showcases the Manhattan method, which encompasses three scenarios for determining the reference particle. In the case where both particles reside in the same cell, an arbitrary tie-breaker is used (such as "furthest to the right" as shown). However, if the particles are in different cells, the reference particle is selected based on its greater Manhattan distance to the boundary of the two cells. The Manhattan method differs significantly from the half-shell method as it leads to a symmetric import volume that is also reduced in size.

# 2.3 FPGA Background

#### 2.3.1 FPGA Architecture

FPGAs are highly versatile integrated circuits that can be configured by users after they are manufactured. They are renowned for their exceptional performance, low power consumption, and support for reconfigurability. FPGAs are widely recognized as the most commonly used reconfigurable devices globally. They offer not only the ability to customize their functionality but also seamless integration into the communication stack, including applications in routers [Bolaria and Byrne, 2009] and network-facing components [Caulfield et al., 2016, Eran et al., 2019].

FPGA normally consists of five types of hardware resources for efficient computation

and communication [Hauck and DeHon, 2008].

- 1. **DSP units** are generally used to perform high-precision and high-performance multiplication, addition, and multiply-accumulation operations.

- 2. **Look-Up-Tables** (**LUTs**) can be used to provide both flexible computation and high-concurrency data storage.

- 3. Flip-Flops (FFs) are used as registers.

- 4. Block RAMs (BRAMs) provide tens of GByte on-chip storage.

- 5. **Multi Gigabit Transceivers** (**MGTs**) provide efficient inter-FPGA communication. Each FPGA chip normally has hundreds of high-bandwidth (over 20Gb/s for each MGT) and low-latency MGTs as I/Os. These I/Os can be directed connected to other on-chip resources.

The hardware resources of FPGAs are organized in a hierarchical and programmable on-chip interconnect network. This allows users to freely integrate these resources and tailor them to their specific problem requirements by programming the interconnect network. The inherent flexibility of FPGAs has positioned them as a highly competitive platform widely utilized in High-Performance Computing (HPC) and machine learning acceleration [Gokhale and Graham, 2005, Herbordt et al., 2007b, Herbordt et al., 2008a, VanCourt and Herbordt, 2009, Benkrid and Vanderbauwhede, 2013].

FPGAs are often compared to GPUs, which are widely used for acceleration purposes. While there are conceptual differences between the two, in practical usage, FPGAs often exhibit similarities to GPUs. FPGAs typically incorporate a large number of parallel computing units, similar to the streaming multiprocessors in GPUs. Each computing unit in an FPGA consists of computation pipelines implemented using LUTs, DSPs, and FFs, as well as local memories utilizing BRAMs and LUTs. BRAMs in FPGAs can also serve as global scratchpad memory, similar to caches in GPUs, which are shared by all computing units.

However, FPGAs also possess distinct advantages and differ from GPUs in several as-