Boston University Theses & Dissertations

http://open.bu.edu

Boston University Theses & Dissertations

2024

# Building next-generation deep learning hardware using photonic computing

https://hdl.handle.net/2144/49259

Downloaded from DSpace Repository, DSpace Institution's institutional repository

## BOSTON UNIVERSITY COLLEGE OF ENGINEERING

#### Dissertation

## BUILDING NEXT-GENERATION DEEP LEARNING HARDWARE USING PHOTONIC COMPUTING

by

#### **CANSU DEMIRKIRAN**

B.Sc., Middle East Technical University, Ankara, Turkey, 2019

Submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

2024

## © 2024 by CANSU DEMIRKIRAN

All rights reserved except for Chapter 3, which is ©2023 by ACM, Chapter 4, which is ©2024 by Springer Nature, and Chapter 5, which is ©2024 by IEEE.

#### Approved by

First Reader

Ajay Joshi, PhD

Professor of Electrical and Computer Engineering

Second Reader

Ayse Coskun, PhD

Professor of Electrical and Computer Engineering

Professor of Systems Engineering

Third Reader

Darius Bunandar, PhD

Chief Scientist Lightmatter

Fourth Reader

Martin Herbordt, PhD

Professor of Electrical and Computer Engineering

Life is short, and the art long, opportunity fleeting, experiment treacherous, and judgment difficult.

– Hippocrates

#### Acknowledgments

First, I would like to express my deepest appreciation and gratitude to my advisor, Prof. Ajay Joshi. His continuous support and guidance throughout my PhD journey have shaped my academic path and always pushed me to achieve more.

I am also deeply thankful to Dr. Darius Bunandar for his invaluable advice and mentorship over the years. I feel incredibly fortunate to have had the opportunity to work directly with him at Lightmatter from the early years of my PhD and for our continued collaboration.

In addition, I extend my gratitude to the rest of my thesis committee members, Prof. Ayse Coskun and Prof. Martin Herbordt, for their precious time, generous support, and insightful feedback.

I am very grateful to all my collaborators and friends from Boston University and Lightmatter. Their contributions have been invaluable to my work.

Furthermore, I greatly appreciate the invaluable friendships I have built over the years in Boston. These friendships have made me feel loved, appreciated, and at home in a foreign country, helping me navigate the hardships of my PhD journey. I would especially like to thank my amazing roommate and all-time cheerleader, Isabel, and my dearest friends Agnieszka, Aleksandra, Ania, Genevieve, and many others for their generous friendships.

I also want to thank Tahir, Emre, Ekin, Malik, Yekta, Deniz, and many other friends and family in Turkey who have kept in touch and supported me despite the distance. Finally, I would like to thank my parents, Aliye and Serdar, for their unconditional love and support.

BUILDING NEXT-GENERATION DEEP LEARNING HARDWARE

USING PHOTONIC COMPUTING

CANSU DEMIRKIRAN

Boston University, College of Engineering, 2024

Major Professor: Ajay Joshi, PhD

Professor of Electrical and Computer Engineering

ABSTRACT

In recent years, the demand for computational power has skyrocketed due to the rapid

advancement of artificial intelligence (AI). As we move past Moore's Law, the limita-

tions of traditional digital computing are pushing the exploration of alternative computing

paradigms. Among the emerging technologies, integrated photonics stands out as a highly

promising candidate for the next generation of high-performance AI computing as it offers

low latency, high bandwidth, and high parallelism. However, there still exist challenges

associated with photonic hardware for AI acceleration including the need for slower and

less efficient electronic circuits and memory units, lack of efficient nonlinearity in photon-

ics, limited precision, analog noise, and various device non-idealities. In this thesis, we

investigate the opportunities and challenges of photonics technology for accelerating state-

of-the-art AI workloads from a realistic perspective, evaluate the performance benefits, and

propose solutions to address the associated challenges.

First, we outline our strategy for designing and evaluating ADEPT, a complete electro-

photonic accelerator for deep neural network (DNN) inference. ADEPT leverages a pho-

tonic computing unit for general matrix-matrix multiplication (GEMM) operations, a vec-

torized digital electronic application-specific integrated circuit (ASIC) for non-GEMM op-

vi

erations, and static random-access memory (SRAM) arrays for storing DNN parameters and activations. Unlike previous photonic DNN accelerators, we adopt a system-level perspective to provide a more realistic assessment of the photonics technology and its applicability in accelerating state-of-the-art DNNs. We detail our design steps and introduce optimizations to minimize the overhead of electronic devices. Our evaluation shows that ADEPT achieves, on average,  $5.73\times$  higher throughput per watt compared to systolic arrays (SAs), and more than  $6.8\times$  and  $2.5\times$  better throughput per watt compared to state-of-the-art electronic and photonic accelerators, respectively.

Second, we focus on the precision limitations in analog computing and propose using the residue number system (RNS) to compose high-precision operations from multiple low-precision operations. This approach eliminates the need for high-precision data converters and avoids information loss. Our study shows that our technology-agnostic RNS-based approach can achieve  $\geq$ 99% of 32-bit floating-point (FP32) accuracy for state-of-the-art DNN inference with only 6-bit and training with 7-bit fixed-point (FXP) arithmetic. This indicates that using RNS can significantly reduce the energy consumption of analog accelerators while maintaining the same throughput and precision. In addition, we present a fault-tolerant dataflow using redundant RNS (RRNS) to protect computations against noise and errors inherent in analog hardware.

At last, leveraging this RNS-based framework, we propose Mirage, a photonic DNN training accelerator. Mirage employs a novel micro-architecture to support modular arithmetic in the analog domain, achieving high energy efficiency without compromising precision. Our study shows that, on average, Mirage achieves FP32 accuracy with 23.8× lower training time and 32.1× lower energy-delay product (EDP) in an iso-energy scenario, and 42.8× less power consumption with comparable or better EDP in an iso-area scenario, compared to SAs.

## **Contents**

| 1 | Intr | Introduction |                                                     |    |

|---|------|--------------|-----------------------------------------------------|----|

|   | 1.1  | Motiv        | ation                                               | 1  |

|   |      | 1.1.1        | AI Model Trends                                     | 1  |

|   |      | 1.1.2        | Technology Scaling and AI Hardware Trends           | 5  |

|   |      | 1.1.3        | Integrated Photonics as a Computing Platform for AI | 7  |

|   | 1.2  | Thesis       | Contribution                                        | 9  |

|   | 1.3  | Organ        | ization                                             | 11 |

| 2 | Bac  | kgroun       | d and Related Work                                  | 12 |

|   | 2.1  | Deep 1       | Neural Networks                                     | 12 |

|   |      | 2.1.1        | DNN Types                                           | 12 |

|   |      | 2.1.2        | Layer Types in DNNs                                 | 14 |

|   |      | 2.1.3        | DNN Inference and Training                          | 18 |

|   |      | 2.1.4        | Data Formats for DNN Execution                      | 19 |

|   | 2.2  | Silicon      | n Photonics Devices                                 | 21 |

|   |      | 2.2.1        | Mach Zehnder Interferometers (MZIs)                 | 21 |

|   |      | 2.2.2        | Microring Resonators (MRRs)                         | 23 |

|   |      | 2.2.3        | Efficiency and Scalability of Photonic Devices      | 24 |

|   |      | 2.2.4        | Device Modulation Mechanisms in Silicon Photonics   | 25 |

|   |      | 2.2.5        | Noise and Errors in Photonics                       | 26 |

|   |      | 2.2.6        | Nonlinear Operations                                | 28 |

|   | 2.3  | The R        | esidue Number System                                | 29 |

|   |      | 2.3.1   | RNS Basics                                         | 29 |

|---|------|---------|----------------------------------------------------|----|

|   |      | 2.3.2   | Forward and Reverse Conversion                     | 29 |

|   |      | 2.3.3   | Redundant RNS                                      | 30 |

|   | 2.4  | Hardw   | are Solutions for DNN Acceleration                 | 31 |

|   |      | 2.4.1   | CMOS-based Platforms                               | 31 |

|   |      | 2.4.2   | Non-CMOS Platforms                                 | 34 |

|   |      | 2.4.3   | Optical Platforms                                  | 35 |

| 3 | Syst | em-Lev  | el Evaluation of Photonic DNN Inference            | 39 |

|   | 3.1  | Photon  | nic Tensor Core Design                             | 39 |

|   |      | 3.1.1   | MZI Array                                          | 40 |

|   |      | 3.1.2   | Photo-core Dataflow                                | 41 |

|   |      | 3.1.3   | Data Conversion                                    | 43 |

|   |      | 3.1.4   | Numerical Precision and Accuracy                   | 44 |

|   |      | 3.1.5   | Photo-core Performance                             | 46 |

|   | 3.2  | Buildin | ng the Full System                                 | 50 |

|   |      | 3.2.1   | Vectorized Processing Unit for Non-GEMM Operations | 50 |

|   |      | 3.2.2   | Memory Units                                       | 52 |

|   |      | 3.2.3   | Performance Optimizations                          | 53 |

|   |      | 3.2.4   | Parallelism                                        | 59 |

|   |      | 3.2.5   | System Performance                                 | 61 |

|   |      | 3.2.6   | Execution Model                                    | 63 |

|   | 3.3  | Relate  | d Work                                             | 64 |

|   |      | 3.3.1   | Electronic Accelerators                            | 64 |

|   |      | 3.3.2   | Photonic Accelerators                              | 65 |

|   | 3.4  | Evalua  | tion Methodology                                   | 66 |

|   |      | 2 / 1   | Architecture level Analyses                        | 66 |

|                                                                     |      | 3.4.2 Circuit- and Device-level Analyses            | 67        |

|---------------------------------------------------------------------|------|-----------------------------------------------------|-----------|

|                                                                     | 3.5  | Discussion                                          | 69        |

|                                                                     | 3.6  | Chapter Summary                                     | 72        |

| 4 Unlocking High-Precision in Analog Tensor Cores via the Residue N |      |                                                     |           |

|                                                                     | Syst | em                                                  | <b>73</b> |

|                                                                     | 4.1  | Precision Challenges in Analog Computing            | 73        |

|                                                                     | 4.2  | RNS-Based Analog DNN Computation                    | 74        |

|                                                                     | 4.3  | RRNS for Fault Tolerance                            | 80        |

|                                                                     | 4.4  | Energy and Area Efficiency                          | 84        |

|                                                                     | 4.5  | Evaluation Methodology                              | 87        |

|                                                                     |      | 4.5.1 Data Converter Energy Estimation              | 87        |

|                                                                     |      | 4.5.2 Accuracy Modeling                             | 87        |

|                                                                     | 4.6  | Related Work                                        | 90        |

|                                                                     | 4.7  | Discussion                                          | 91        |

|                                                                     | 4.8  | Chapter Summary                                     | 92        |

| 5                                                                   | RNS  | S-based Photonic DNN Training Accelerator Design    | 93        |

|                                                                     | 5.1  | RNS-Based Dataflow in Mirage                        | 93        |

|                                                                     | 5.2  | Modular Arithmetic with Photonics                   | 96        |

|                                                                     |      | 5.2.1 Modular Multiplication Unit (MMU)             | 96        |

|                                                                     |      | 5.2.2 Modular Dot Product Unit (MDPU) and MMVMU     | 01        |

|                                                                     |      | 5.2.3 Phase Detection Unit                          | .02       |

|                                                                     | 5.3  | Moduli Selection                                    | .03       |

|                                                                     | 5.4  | Mirage Accelerator Design                           | 04        |

|                                                                     | 5.5  | Sensitivity Analysis                                | .05       |

|                                                                     |      | 5.5.1 BFP Parameters                                | 06        |

|                                                                     |      | 5.5.2 Choice of the Array Size and Number of Arrays | .06       |

| 5.6                                      | Accuracy Results                                                                       |                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.7 Performance, Power, and Area Results |                                                                                        | mance, Power, and Area Results                                                                                                                                                                         | . 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.8                                      | Evalua                                                                                 | tion Methodology                                                                                                                                                                                       | . 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                          | 5.8.1                                                                                  | Accuracy Modeling                                                                                                                                                                                      | . 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                          | 5.8.2                                                                                  | Hardware Performance, Power and Area                                                                                                                                                                   | . 116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.9                                      | Relate                                                                                 | d Work                                                                                                                                                                                                 | . 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.10                                     | Discus                                                                                 | sion                                                                                                                                                                                                   | . 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.11                                     | Chapte                                                                                 | er Summary                                                                                                                                                                                             | . 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Sum                                      | mary a                                                                                 | nd Future Work                                                                                                                                                                                         | 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.1                                      | Summ                                                                                   | ary of Contributions                                                                                                                                                                                   | . 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.2                                      | Curren                                                                                 | t Limitations and Future Research Directions                                                                                                                                                           | . 124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                          | 6.2.1                                                                                  | Device-Level Challenges                                                                                                                                                                                | . 124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                          | 6.2.2                                                                                  | Routing and Integration Challenges                                                                                                                                                                     | . 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                          | 6.2.3                                                                                  | Data Conversion Challenges                                                                                                                                                                             | . 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                          | 6.2.4                                                                                  | Scaling Challenges                                                                                                                                                                                     | . 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                          | 6.2.5                                                                                  | Performance Modeling Challenges                                                                                                                                                                        | . 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                          | 6.2.6                                                                                  | Challenges around RNS-Based DNN Computation                                                                                                                                                            | . 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                          | 6.2.7                                                                                  | Future of Photonic Computing                                                                                                                                                                           | . 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.3                                      | Final F                                                                                | Remarks                                                                                                                                                                                                | . 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Appe                                     | endix                                                                                  |                                                                                                                                                                                                        | 134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <b>A.</b> 1                              | Error d                                                                                | distribution in the RRNS code space                                                                                                                                                                    | . 134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| A.2                                      | Extend                                                                                 | led Dynamic Range via Positional Number System                                                                                                                                                         | . 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| feren                                    | ces                                                                                    |                                                                                                                                                                                                        | 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| rricu                                    | lum Vit                                                                                | tae                                                                                                                                                                                                    | 163                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                          | 5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>Sum<br>6.1<br>6.2<br>6.3<br>Apperature A.1<br>A.2 | 5.7 Perform 5.8 Evaluation 5.8.1 5.8.2 5.9 Related 5.10 Discuss 5.11 Chapter 5.11 Summ 6.2 Current 6.2.1 6.2.2 6.2.3 6.2.4 6.2.5 6.2.6 6.2.7 6.3 Final F  Appendix A.1 Error of A.2 Extending ferences | 5.7 Performance, Power, and Area Results 5.8 Evaluation Methodology 5.8.1 Accuracy Modeling 5.8.2 Hardware Performance, Power and Area 5.9 Related Work 5.10 Discussion 5.11 Chapter Summary  Summary and Future Work 6.1 Summary of Contributions 6.2 Current Limitations and Future Research Directions 6.2.1 Device-Level Challenges 6.2.2 Routing and Integration Challenges 6.2.3 Data Conversion Challenges 6.2.4 Scaling Challenges 6.2.5 Performance Modeling Challenges 6.2.6 Challenges around RNS-Based DNN Computation 6.2.7 Future of Photonic Computing 6.3 Final Remarks  Appendix A.1 Error distribution in the RRNS code space A.2 Extended Dynamic Range via Positional Number System |

## **List of Tables**

| 2.1 | Device modulation mechanisms and corresponding device metrics in sili-           |

|-----|----------------------------------------------------------------------------------|

|     | con photonics modulators                                                         |

| 3.1 | Comparison against state-of-the-art electronic and photonic accelerators 65      |

| 3.2 | Comparison against state-of-the-art photonic accelerators                        |

| 4.1 | Data and data converter precision in RNS-based, LP FXP, and HP FXP               |

|     | analog cores                                                                     |

| 4.2 | MLPerf (Inference: Datacenters) benchmarks (Reddi et al., 2020) 78               |

| 4.3 | Validation accuracy results after training/fine-tuning                           |

| 5.1 | Validation accuracy of Mirage and various data formats (Zhang et al., 2022b).112 |

| 5.2 | Performance, power, and area analysis of MAC units                               |

| 5.3 | Mirage versus DNN inference accelerators                                         |

## **List of Figures**

| 1.1 | Select AI Index technical performance benchmarks vs. human perfor-                      |    |

|-----|-----------------------------------------------------------------------------------------|----|

|     | mance, based on data from the 2024 Stanford AI Index Report (Maslej                     |    |

|     | et al., 2024)                                                                           | 2  |

| 1.2 | Training compute of notable AI models over time. The figure is taken from               |    |

|     | Epoch AI's 2023 study (Epoch AI, 2023)                                                  | 3  |

| 1.3 | Number of trainable parameters in notable AI models over time. The figure               |    |

|     | is taken from Epoch AI's 2023 study (Epoch AI, 2023)                                    | 4  |

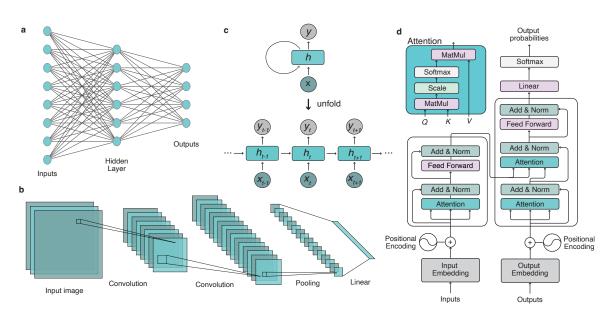

| 2.1 | (a) MLP architecture. (b) CNN architecture. (c) RNN architecture. (d)                   |    |

|     | Transformer architecture                                                                | 13 |

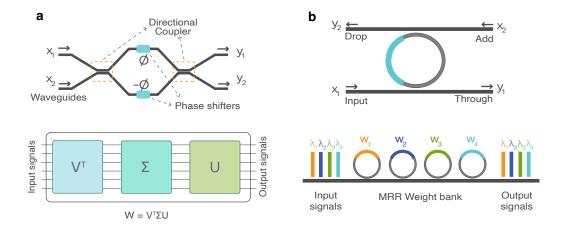

| 2.2 | (a) MZI and MZI-based matrix-vector operation. (b) MRR and MRR-                         |    |

|     | based weight bank.                                                                      | 22 |

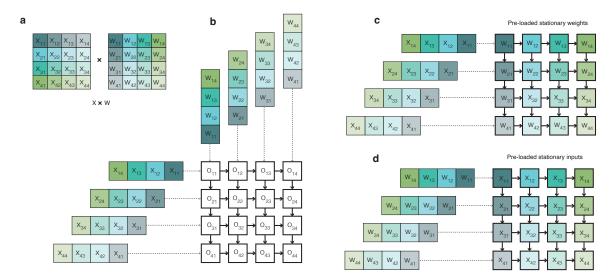

| 2.3 | (a) Matrix multiplication between $4 \times 4$ input matrix $X$ and $4 \times 4$ weight |    |

|     | matrix W. (b) OS dataflow. (c) WS dataflow. (d) IS dataflow                             | 33 |

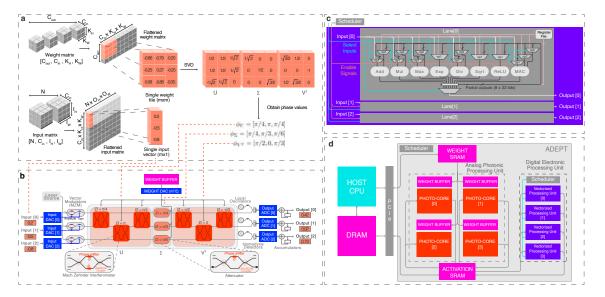

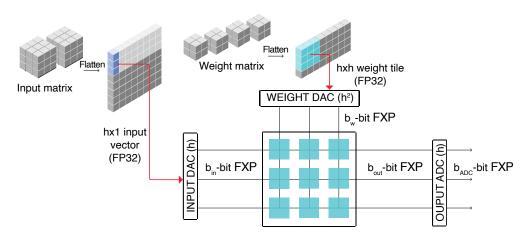

| 3.1 | Diagram showing different components of ADEPT and how operations are                    |    |

|-----|-----------------------------------------------------------------------------------------|----|

|     | performed. (a) Example GEMM operation in the photo-core. (b) Program-                   |    |

|     | ming input and weight matrices into the photo-core. The $h \times h$ (here $h = 3$      |    |

|     | as an example) photo-core consists of $2 \times h(h-1)/2 = 6$ MZIs (for $U$             |    |

|     | and $V^T$ ) and 3 attenuators (for $\Sigma$ ). (c) Microarchitecture for a single digi- |    |

|     | tal electronic vectorized processing unit. The unit comprises $h=3$ digital             |    |

|     | lanes, each consisting of arithmetic units to perform non-GEMM opera-                   |    |

|     | tions. (d) Full system architecture including the host CPU, the DRAM, and               |    |

|     | ADEPT—interconnected using a PCI-e interface. As an example, we show                    |    |

|     | four photo-cores and four vectorized processing units                                   | 42 |

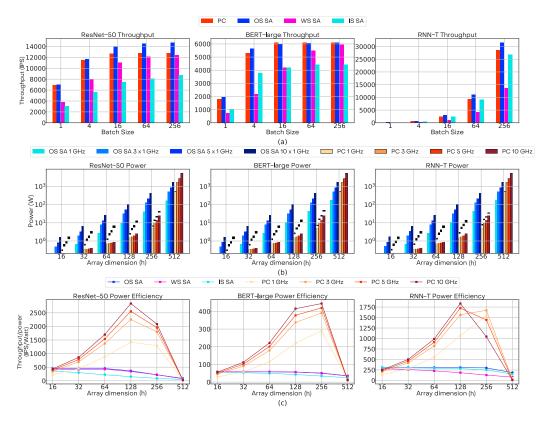

| 3.2 | (a) Throughput vs. batch size of $128 \times 128$ photo-core (PC) and SA with           |    |

|     | three dataflows at 1 GHz clock. (b) Power consumption of the OS SA and                  |    |

|     | the WS photo-core for different array sizes and clock frequencies. Laser                |    |

|     | power is shown with solid color, ADCs/DACs with the white diagonal pat-                 |    |

|     | tern, and E-to-O/O-to-E conversion with the black diagonal pattern. (c)                 |    |

|     | Power efficiency of SAs and photo-core for different array sizes and clock              |    |

|     | frequencies                                                                             | 47 |

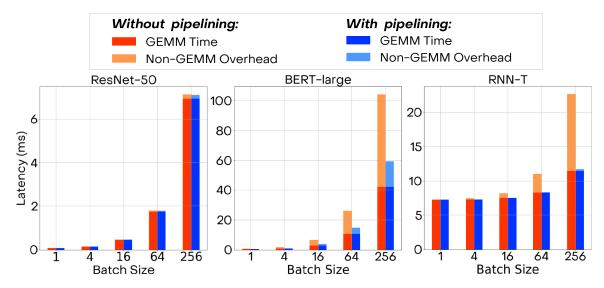

| 3.3 | Latency of ADEPT with a $128 \times 128$ photo-core operating at 10 GHz clock           |    |

|     | with and without pipelining the GEMM and non-GEMM operations. Here                      |    |

|     | the latency is for one batch of inputs for three networks. The results are              |    |

|     | calculated for varying batch sizes.                                                     | 54 |

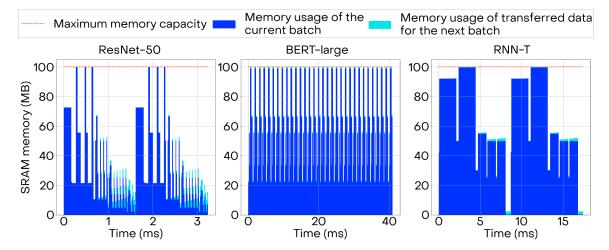

| 3.4 | Activation SRAM usage for computing on the current batch of inputs along            |    |

|-----|-------------------------------------------------------------------------------------|----|

|     | with data transfer for the next batch of inputs within ADEPT. Both input            |    |

|     | and output activations for the current batch must be stored in the activation       |    |

|     | SRAM (dark blue) while the input data are transferred for the next batch            |    |

|     | (light blue). A $128 \times 128$ photo-core at 10 GHz clock is used with batch      |    |

|     | sizes of 58, 88, and 50 for ResNet-50, BERT-large, and RNN-T, respec-               |    |

|     | tively to fully use the 100 MB activation SRAM capacity                             | 56 |

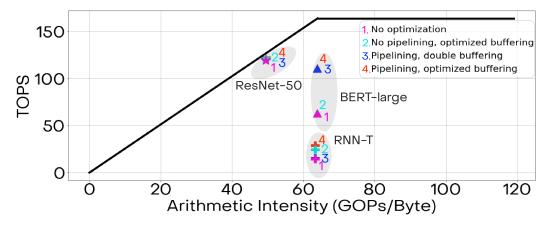

| 3.5 | Roofline plot showing the effect of optimizations on ADEPT with a single            |    |

|     | $128 \times 128$ photo-core. The arithmetic intensity is calculated using MAC       |    |

|     | operations over activation SRAM reads/writes                                        | 59 |

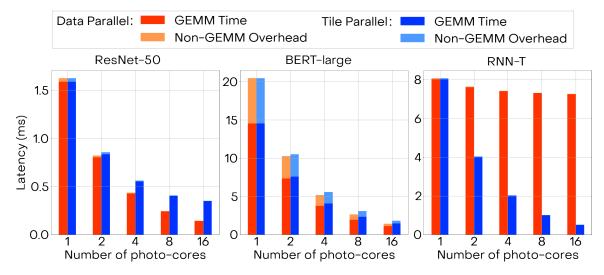

| 3.6 | Latency of ADEPT ( $128 \times 128$ photo-core at 10 GHz clock) when execut-        |    |

|     | ing the three neural networks with different photo-core counts using data           |    |

|     | and tile parallelism                                                                | 60 |

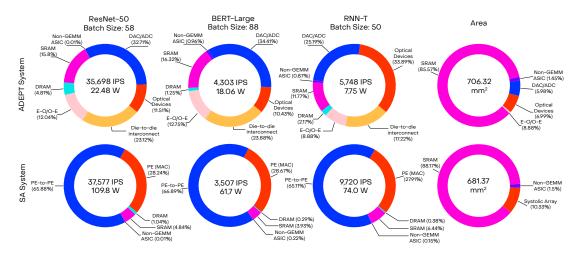

| 3.7 | Average total (static and dynamic) power distribution and area distribution         |    |

|     | of ADEPT (128 $\times$ 128, 10 GHz photo-core) and the SA system (128 $\times$ 128, |    |

|     | 10×1 GHz array, OS dataflow)                                                        | 62 |

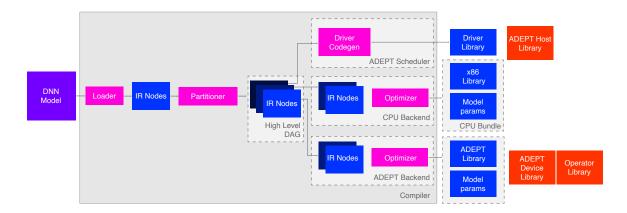

| 3.8 | Compilation process of an ML model for ADEPT                                        | 64 |

| 4.1 | Dataflow for a conventional analog core                                             | 75 |

|     |                                                                                     | 13 |

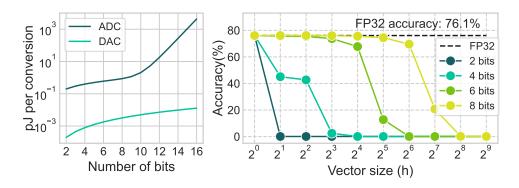

| 4.2 | (a) Energy consumption per conversion for DACs and ADCs. (b) Accuracy               |    |

|     | degradation in ResNet50 on Imagenet in a conventional analog core                   | 75 |

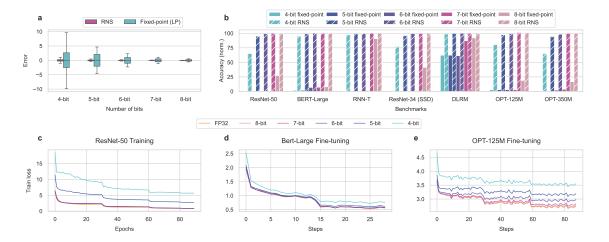

| 4.3 | (a) The distribution of average error observed at the output of a dot product                                                 |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------|----|

|     | performed with the RNS-based analog approach (pink) and the LP regular                                                        |    |

|     | FXP analog approach (cyan). Error is defined as the distance from the re-                                                     |    |

|     | sult calculated in FP32. The experiments are repeated for 10,000 randomly                                                     |    |

|     | generated vector pairs with a vector size of $h = 128$ . The center lines of                                                  |    |

|     | the boxes represent the median. The boxes extend between the first and the                                                    |    |

|     | third quartile of the data, while whiskers extend $1.5\times$ of the inter-quartile                                           |    |

|     | range from the box. (b) Inference accuracy of regular FXP (LP) and RNS-                                                       |    |

|     | based cores (See Table 4.1) on MLPerf (Inference: Datacenters) bench-                                                         |    |

|     | marks. The accuracy numbers are normalized by the accuracy achieved                                                           |    |

|     | in FP32. (c-e) Loss during training for FP32 and the RNS-based approach                                                       |    |

|     | with varying moduli bit-width. ResNet-50 (c) is trained from scratch for 90                                                   |    |

|     | epochs. BERT-Large (d) and OPT-125M (e) are fine-tuned from pre-trained                                                       |    |

|     | models for 2 and 3 epochs, respectively                                                                                       | 77 |

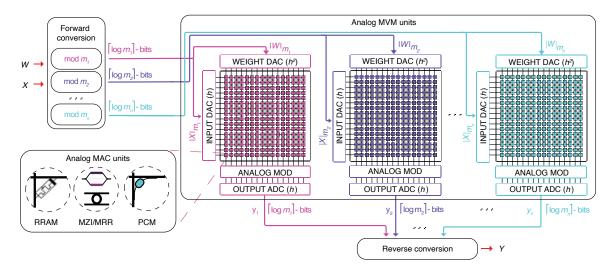

| 4.4 | RNS-based analog GEMM dataflow. The operation is shown for a moduli                                                           |    |

|     | set $\mathcal{M} = \{m_1, \dots, m_n\}$ . The $n \ h \times h$ analog MVM units are represented as                            |    |

|     | generic blocks for $n$ moduli. The dataflow is agnostic to the underlying                                                     |    |

|     | analog technology.                                                                                                            | 79 |

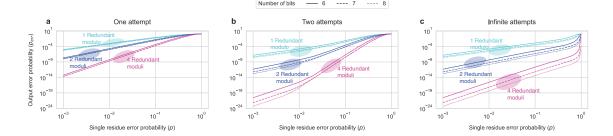

| 4.5 | Calculated output error probability (perr) versus single residue error prob-                                                  |    |

|     | ability ( <b>p</b> ). <b>a-c</b> $p_{err}$ for one ( <b>a</b> ), two ( <b>b</b> ), and infinite ( <b>c</b> ) error correction |    |

|     | attempts and a varying number of redundant moduli $(k)$                                                                       | 81 |

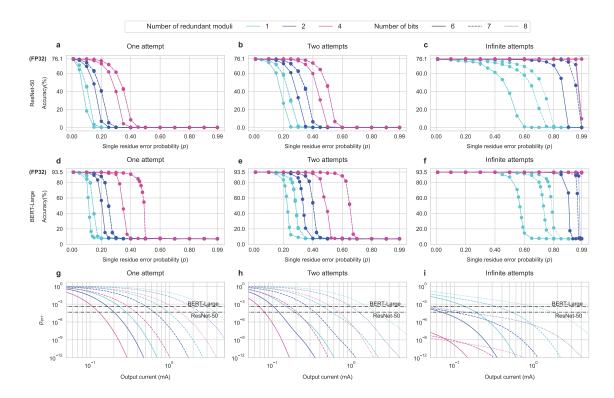

| 4.6 | (a-f) The plots show ResNet-50 (a-c) and BERT-Large (d-f) inference ac-           |     |

|-----|-----------------------------------------------------------------------------------|-----|

|     | curacy under varying $p$ for RRNS with one (a and d), two (b and e), and          |     |

|     | infinite (c and f) error correction attempts and a varying number of redun-       |     |

|     | dant moduli $(k)$ . $(g-i)$ $p_{err}$ caused by shot and thermal noise versus the |     |

|     | output current at the photodetector in an analog photonic accelerator for         |     |

|     | RRNS with one (g), two (h), and infinite (i) error correction attempts and        |     |

|     | varying $k$ . The horizontal black lines show the cut-off points where larger     |     |

|     | $p_{err}$ starts degrading the accuracy for the evaluated DNNs (i.e., ResNet-50   |     |

|     | and BERT-Large)                                                                   | 82  |

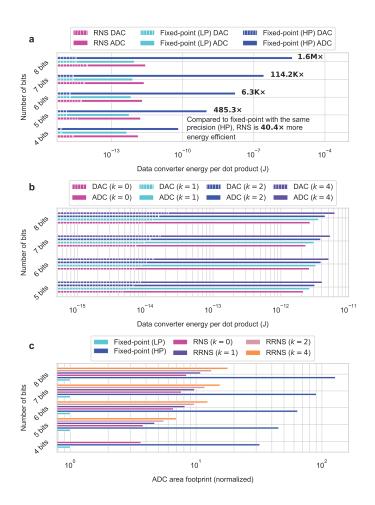

| 4.7 | (a-b) Energy consumption of DACs and ADCs per dot product for the                 |     |

|     | RNS-based and the regular FXP (a) and the RNS and RRNS-based ana-                 |     |

|     | log approaches (b). (c) Normalized area of ADCs for the FXP, RNS, and             |     |

|     | RRNS-based approaches                                                             | 85  |

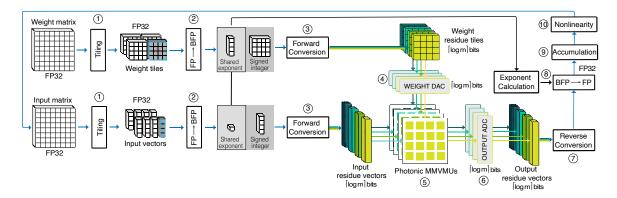

| 5.1 | Mirage's RNS-based dataflow for a single tiled-MVM operation as part of           |     |

|     | a forward pass. We show a four-moduli case in this figure as an example           | 94  |

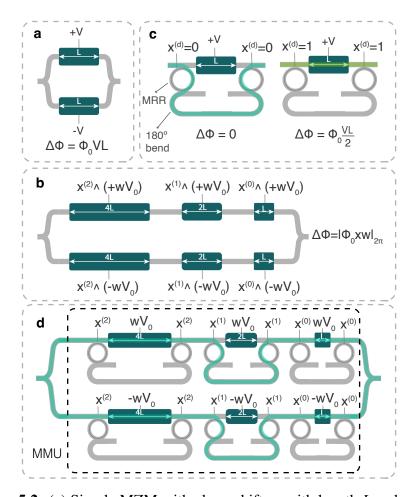

| 5.2 | (a) Simple MZM with phase shifters with length $L$ and applied voltage $V$ .      |     |

|     | (b) 3-bit modular multiplication using cascaded phase shifters. (c) Routing       |     |

|     | light using MRR switches. (d) 3-bit modular multiplication using MRR              |     |

|     | switches                                                                          | 98  |

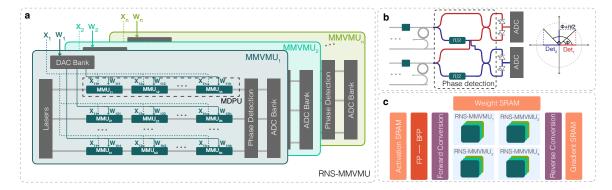

| 5.3 | (a) RNS-MMVMU micro-architecture. (b) Phase detection unit. The top               |     |

|     | arms of the two rows detect the amplitude of the incoming signals directly        |     |

|     | while the bottom arms apply $\pi/2$ radians phase shift and detect the am-        |     |

|     | plitude. Phase detection is done by using these two amplitude values. (c)         |     |

|     | Main components of Mirage architecture with four RNS-MMVMUs and                   |     |

|     | three moduli as an example                                                        | 102 |

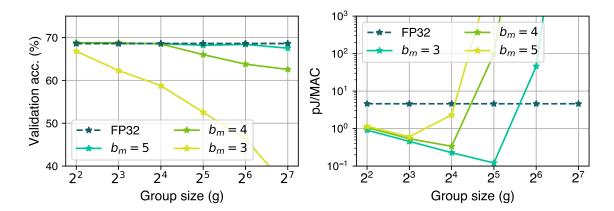

| 5.4 | (a) ResNet18 validation accuracy on Imagenet after training from scratch         |     |

|-----|----------------------------------------------------------------------------------|-----|

|     | for 60 epochs and (b) energy per MAC operation (pJ/MAC) for varying              |     |

|     | $b_m$ and $g$ . This analysis includes energy consumed by lasers and tuning      |     |

|     | circuitry, TIAs, DACs and ADCs, FP-BFP, and RNS-BNS conversions.                 |     |

|     | Here, ResNet18 is shown as an example. We observed similar behavior for          |     |

|     | other evaluated DNNs                                                             | 107 |

| 5.5 | (a) Number of MDPUs versus spatial utilization (%). (b) Number of RNS-           |     |

|     | MMVM units versus spatial utilization (%)                                        | 108 |

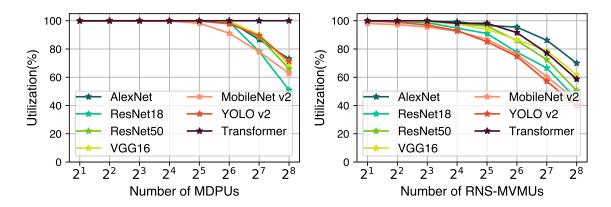

| 5.6 | (a) Latency per step for each layer of AlexNet for Mirage (left) and a 1         |     |

|     | GHz digital systolic array (right). (b) Latency per step for different DNNs      |     |

|     | and impact of dataflow for Mirage (left) and a 1 GHz digital systolic array      |     |

|     | (right). The numbers for all dataflows are normalized to the DF1 results for     |     |

|     | all models                                                                       | 109 |

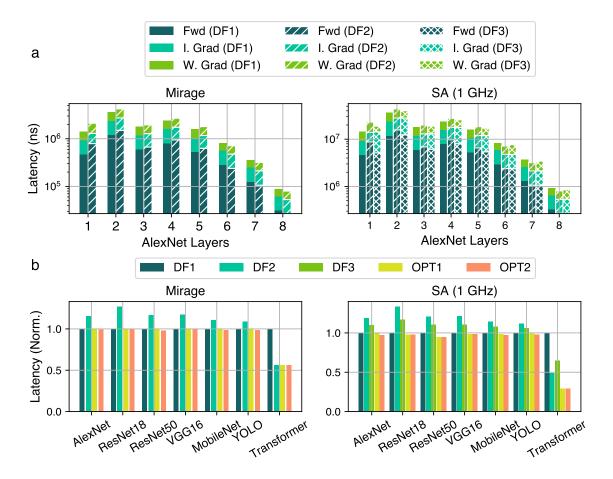

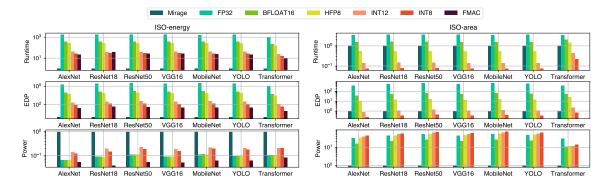

| 5.7 | Normalized training runtime, EDP and power comparison of Mirage (eight           |     |

|     | $16 \times 32$ arrays) against systolic arrays using MAC units with various data |     |

|     | formats. The plots on the left-hand side show the iso-energy results where       |     |

|     | the number of MAC units in the systolic arrays is scaled to consume the          |     |

|     | same energy per MAC operations using the numbers in Table 5.2. The plots         |     |

|     | on the right-hand side show iso-area results where the number of MAC             |     |

|     | units in the systolic arrays is scaled to take up the same area as Mirage. As    |     |

|     | we do not have the area footprint of the FMAC units, we do not show the          |     |

|     | FMAC numbers in the iso-area results                                             | 113 |

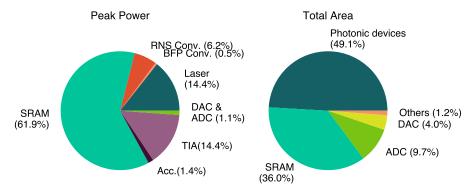

| 5.8 | Peak power consumption and area breakdown for Mirage. The total peak             |     |

|     | nower consumption is 19.95 W and the total area is 476 6mm <sup>2</sup>          | 115 |

## **List of Abbreviations**

| ADC          | <br>Analog-to-Digital Converter             |

|--------------|---------------------------------------------|

| AI           | <br>Artificial Intelligence                 |

| ASIC         | <br>Application-Specific Integrated Circuit |

| A-to-D       | <br>Analog-to-Digital                       |

| BFP          | <br>Block Floating Point                    |

| BF16         | <br>Brain Floating Point 16-bit             |

| BMM          | <br>Batched Matrix Multiplication           |

| BNS          | <br>Block Number System                     |

| CiM          | <br>Compute in Memory                       |

| CMOS         | <br>Complementary Metal-Oxide-Semiconductor |

| CNN          | <br>Convolutional Neural Network            |

| CPU          | <br>Central Processing Unit                 |

| CRT          | <br>Chinese Remainder Theorem               |

| DAC          | <br>Digital-to-Analog Converter             |

| DAG          | <br>Directed Acyclic Graph                  |

| DNN          | <br>Deep Neural Network                     |

| $D^2NN$      | <br>Diffractive Neural Networks             |

| DOE          | <br>Diffractive Optical Element             |

| DPU          | <br>Digital Processing Unit                 |

| DRAM         | <br>Dynamic RAM                             |

| D-to-A       | <br>Digital-to-Analog                       |

| <b>ECRAM</b> | <br>Electrochemical Random Access Memory    |

| EDP          | <br>Energy-Delay Product                    |

| EM           | <br>Electromagnetic                         |

| E-to-O       | <br>Electrical-to-Optical                   |

| FC           | <br>Fully Connected                         |

| FeFET        | <br>Ferroelectric Field-Effect Transistor   |

| FHE          | <br>Fully Homomorphic Encryption            |

| FoM          | <br>Figure of Merit                         |

| FP           | <br>Floating Point                          |

| FP16         | <br>16-bit Floating Point                   |

| FP32         | <br>32-bit Floating Point                   |

|              |                                             |

FPGA ..... Field-Programmable Gate Array

FXP ..... Fixed Point

GELU ..... Gaussian Error Linear Unit

GEMM .... General Matrix Multiplication

Ge-on-Si Germanium-on-Silicon

GPU Graphics Processing Unit

GRU Gated Recurrent Unit

HP ..... High Precision

IC Integrated Circuit

IM2COL Image to Column

INT8 8-bit Integer

IPS ..... Inferences Per Second

IPS/W ..... Inferences Per Second per Watt

IS ..... Input Stationary

LLVM ..... Large Language Model

LLVM ..... Low-Level Virtual Machine

LP ..... Low Precision

LSB ..... Least Significant Bit

LSTM ..... Long Short-Term Memory

LUT ..... Look-Up Table

MACMultiply-AccumulateMDPUModular Dot Product UnitMLPMulti-Layer PerceptronMMUModular Multiplication Unit

MMVMU ..... Modular MVM Unit

MOEMS ..... Micro-Opto-Electro-Mechanical Systems

MRR ..... Microring Resonator

MVMMatrix-Vector MultiplicationMZIMach-Zehnder InterferometerMZMMach-Zehnder ModulatorNLPNatural Language Processing

NOEMS ...... Nano-Opto-Electro-Mechanical Systems

NVM Non-Volatile Memory

OP/s Operations per Second

OS Output Stationary

O-to-E Optical-to-Electrical

PCI-e ..... Peripheral Component Interconnect Express

PDK ..... Process Design Kit

PDF ..... Probability Distribution Function

PE ..... Processing Element

| PiM      | <br>Processing in Memory              |

|----------|---------------------------------------|

| PNS      | <br>Positional Number System          |

| QAT      | <br>Quantization-Aware Training       |

| RAM      | <br>Random-Access Memory              |

| ReLU     | <br>Rectified Linear Unit             |

| RNN      | <br>Recurrent Neural Network          |

| RNS      | <br>Residue Number System             |

| RRAM     | <br>Resistive RAM                     |

| RRNS     | <br>Redundant Residue Number System   |

| RTL      | <br>Register Transfer Level           |

| SA       | <br>Systolic Array                    |

| SAR      | <br>Successive Approximation Register |

| SGD      | <br>Stochastic Gradient Descent       |

| SiN      | <br>Silicon Nitride                   |

| SLM      | <br>Spatial Light Modulator           |

| SNR      | <br>Signal-to-Noise Ratio             |

| SOA      | <br>Semiconductor Optical Amplifier   |

| SOT-MRAM | <br>Spin-Orbit Torque Magnetic RAM    |

| SRAM     | <br>Static RAM                        |

| STT-MRAM | <br>Spin-Transfer Torque Magnetic RAM |

| SVD      | <br>Singular Value Decomposition      |

| TIA      | <br>Transimpedance Amplifier          |

| TOPS     | <br>Tera Operations per Second        |

| TPU      | <br>Tensor Processing Unit            |

| WDM      | <br>Wavelength-Division Multiplexing  |

| WS       | <br>Weight Stationary                 |

|          |                                       |

### Chapter 1

### Introduction

#### 1.1 Motivation

#### 1.1.1 AI Model Trends

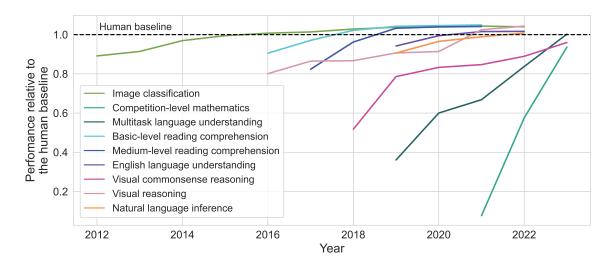

Artificial intelligence (AI) has become pervasive in today's world, influencing numerous aspects of daily life and various industries. Deep neural networks (DNNs) are at the heart of this AI revolution, with a broad spectrum of applications, including language processing (Brown et al., 2020; Team et al., 2023; Touvron et al., 2023; Devlin et al., 2018; Zhang et al., 2022a), computer vision (He et al., 2016; Redmon et al., 2016), healthcare (Rajpurkar et al., 2017; Shen et al., 2019), coding (Chen et al., 2021; Feng et al., 2020b; Gupta et al., 2017), audio processing (Amodei et al., 2016; Van Den Oord et al., 2016), robotics (Levine et al., 2018; Mnih et al., 2016), and many others. Figure 1·1 illustrates the progress of AI systems relative to human baselines across nine benchmarks, each corresponding to a different task. This plot demonstrates that AI capabilities have already surpassed human performance, especially in visual tasks.

This progress, however, comes with a significant cost. While the progress trajectory of AI models is influenced by many factors, there is a strikingly consistent correlation between the amount of compute in AI models and their capabilities, which makes compute a quantifiable proxy for measuring progress in AI research (Kaplan et al., 2020; Hestness et al., 2017; Li et al., 2020).

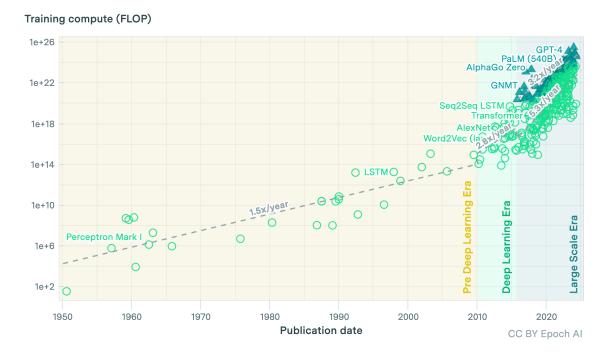

A recent study (Sevilla et al., 2022) explored AI compute trends and divided the history of AI models into three distinct eras, as illustrated in Figure 1.2:

**Figure 1.1:** Select AI Index technical performance benchmarks vs. human performance, based on data from the 2024 Stanford AI Index Report (Maslej et al., 2024)

- The Pre-Deep Learning Era: Before the advent of deep learning, training compute requirements roughly followed Moore's Law, doubling approximately every 20 months.

- The Deep Learning Era: Beginning around 2010, there has been a dramatic acceleration in compute requirements, with a doubling time of roughly 6 months.

- The Large-Scale Era: Starting from 2015, this era is marked by the development of models that used two-to-three orders of magnitude more compute than those in the Deep Learning Era. However, the compute growth for these large-scale models has a relatively slower doubling time of about 10 months.

Although the doubling time in the Large-Scale Era appears relatively slower, it remains extraordinarily rapid. Figure 1·2 shows the amount of training compute in notable AI models over time. Since 2010, the amount of training compute for AI models has increased by a factor of 10 billion, far outpacing Moore's Law (Sevilla et al., 2022).

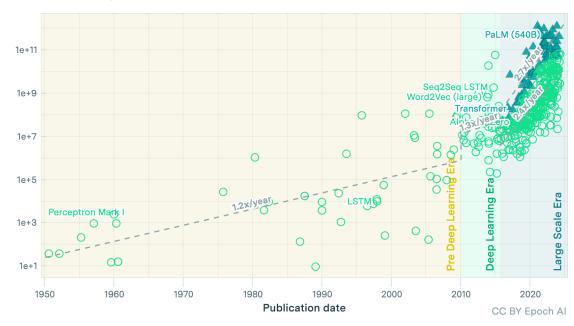

The number of parameters is another important metric correlated with AI capabilities,

**Figure 1.2:** Training compute of notable AI models over time. The figure is taken from Epoch AI's 2023 study (Epoch AI, 2023).

which greatly impacts the compute and memory requirements in AI systems. Figure 1·3 shows the increase in the number of trainable parameters in notable AI models over time for the three eras of AI compute. The largest models available today include more than a trillion trainable parameters.

This increasing trend in compute requirements and model sizes of models places significant stress on today's AI systems, necessitating faster compute cores, higher data bandwidths, and improved interconnect speeds. Supporting these large models also results in very high power consumption, significantly escalating their environmental footprint. For instance, Meta's Llama 2 model with 70 billion parameters is reported to release 291.2 tonnes of carbon during training while consuming 400 MWh of power. This carbon emission is nearly 291× more than the emissions from a round-trip flight from New York to San Francisco for one traveler, and roughly 16× more than the annual carbon footprint of an average American (Touvron et al., 2023). Similarly, GPT-3 is reported to consume 1,287

#### Number of trainable parameters

**Figure 1.3:** Number of trainable parameters in notable AI models over time. The figure is taken from Epoch AI's 2023 study (Epoch AI, 2023).

MWh of power and emit 502 tonnes of carbon (Maslej et al., 2024). While the emissions from individual inference queries may be relatively low, the total impact can surpass that of training when models are queried thousands or even millions of times daily. Although the prominent developers of AI models such as OpenAI, Google, Anthropic, and Mistral do not disclose their carbon footprint, their recent models with over a trillion parameters are expected to go well beyond the aforementioned numbers (Maslej et al., 2024). Hence, beyond speed, improvements in energy efficiency are also crucial.

The current trend of escalating compute and energy requirements and model sizes is unsustainable with existing technology, both in terms of performance and environmental impact. The massive power consumption and carbon emissions associated with training and deploying large-scale models underscore the critical need for innovation and advancements in both hardware and software design. These innovations are crucial to ensure continued progress in AI, driving advancements in numerous fields such as healthcare, education, and

finance.

#### 1.1.2 Technology Scaling and AI Hardware Trends

For decades, processor performance improvements have been guided by Moore's Law, which states that the number of transistors in integrated circuits (ICs) doubles approximately every two years, driven by the continuous reduction in transistor dimensions through advancements in complementary metal-oxide-semiconductor (CMOS) technology. Alongside Moore's Law, Dennard scaling (Bohr, 2007) suggested that as transistors become smaller, their power consumption decreases proportionally to their area. However, as transistor sizes reached the nanometer scale, this power scaling decoupled from the device area due to physical constraints, leading to increased power consumption per unit area (Gargini, 2023). This phenomenon created the so-called *power wall*, limiting the increase in clock frequencies and posing a significant challenge to performance scaling. The rising transistor densities given a power budget led to dark silicon (Esmaeilzadeh et al., 2011), where parts of the IC are powered down to manage heat and power consumption. Techniques like dynamic voltage and frequency scaling (Le Sueur and Heiser, 2010) can offer partial mitigation, but the root problem persists at the device level.

Despite the power wall impeding performance scaling, the demand for high-performance execution of complex workloads continued to grow. In response to the breakdown of Dennard scaling, architects increased the number of logical cores in general-purpose processors and exploited parallelism at various levels. However, the benefits of large core counts are constrained by memory bottlenecks in a Von Neumann execution model, even when the workload offers a high degree of parallelism.

To boost performance further, architects have adopted heterogeneous computing frameworks, offloading critical tasks to hardware accelerators. These specialized co-processors, tailored for specific applications, outperform general-purpose processors in terms of throughput and energy efficiency. By bypassing the limitations of the Von Neumann architec-

ture, accelerators achieve high levels of parallelism and concurrency, effectively mitigating memory bottlenecks and enhancing compute density and energy efficiency. Today, modern AI hardware largely depends on these accelerators, such as graphic processing units (GPUs) and application-specific integrated circuits (ASICs).

A recent study (Hobbhahn et al., 2023) reports that GPUs have seen an energy efficiency doubling time of around 2.7 years over the past 15 years when using the 32-bit floating point (FP32) format. Moreover, adopting more efficient data formats and lower numeric precision has remarkably enhanced AI workload performance in recent years. For instance, NVIDIA's H100 GPU achieves speedups of approximately 7× with tensor-FP32, 15× with tensor-FP16, and 30× with 8-bit integer (INT8) compared to FP32 (Hobbhahn et al., 2023). Today, the highest-performing GPU, NVIDIA B200 SXM, has a 2.25e15 operations per second (OP/s) peak throughput in tensor-FP16 and 4.5e15 OP/s in INT8 (NVIDIA Corporation, 2024b).

ASICs like Google's Tensor Processing Unit (TPU), on the other hand, typically rely on systolic array (SA)-based architectures. SAs involve an array of processing elements (PEs), each connected to its neighbors. Each PE has a multiply-accumulate (MAC) unit along with local buffers to store inputs and outputs. Depending on the dataflow, data moves from one side of the SA to the other as MAC operations are performed. This structure, which has been used in many AI accelerators (Chen et al., 2016; Chen et al., 2019; Lee et al., 2018; Jouppi et al., 2017), enables data reuse and maximizes the energy efficiency in general matrix-matrix multiplication (GEMM) operations. Today, the most recent TPU (vp5) has a 4.59e14 OP/s peak throughput in Brainfloat-16 (BF16) (Google Cloud, 2024).

In recent years, there have been remarkable advancements in GPU and ASIC designs, maintaining an exponential trend in their performance improvements. However, these gains are largely due to specialization, the adoption of efficient data formats, and hardware-software co-design rather than technology scaling. As the benefits of specialization begin

to saturate and CMOS technology approaches its physical limits, performance improvements in CMOS-based hardware are expected to plateau. Given the rapid growth of AI workloads, engineers and researchers must seek alternative solutions to sustain the growth in AI capabilities.

#### 1.1.3 Integrated Photonics as a Computing Platform for AI

The idea of computing with light is not new and has been explored starting from the 1960s (Reimann and Kosonocky, 1965). Replacing traditional CMOS-based transistors with optical transistors has been an appealing idea because of the high speed, bandwidth, and unique parallelism opportunities that light signals inherently offer. As a result, free-space optical computers have remained a major research interest over many decades (Bell, 1986; Caulfield, 1987; Hsu et al., 1988; Bernstein et al., 2021). However, these optical computers have not been widely adopted due to challenges associated with optical alignment, precision control over the phase and amplitude of the light field, and the limited component count that could not compete with digital electronics.

The advent of integrated photonics has largely solved the problem of controlling and stabilizing many photonic components, offering greater compactness for high integration compared to other photonic computing schemes. One particular flavor of integrated photonics, silicon photonics, has seen widespread integration in commercial CMOS foundries alongside CMOS transistors (Giewont et al., 2019). Validated process design kits (PDKs) developed by various foundries have pushed integrated photonics towards standardization, ensuring reliable performance and accessibility for designers and users (Ning et al., 2024). Consequently, many recent works leverage the highly parallel and efficient linear transformations enabled by silicon photonics to develop specialized DNN accelerators. These accelerators have demonstrated promising results, with orders of magnitude improvements in speed and energy efficiency compared to their electrical counterparts (Shen et al., 2017; Shiflett et al., 2021; Bangari et al., 2019; Shiflett et al., 2020; Peng et al., 2020; Wu et al.,

- 2021; Wetzstein et al., 2020; Shastri et al., 2021). Despite these promising results, several challenges remain in building photonic AI systems with current technology. We categorize the primary issues under two groups:

- 1. The need for electronic components in photonic DNN acceleration: The limitations of weak photon-photon nonlinearities and the lack of photonic information storage present significant challenges in designing practical general-purpose optical computing systems. The lack of efficient nonlinearity in photonics has led researchers to focus on developing specialized photonic units for GEMM operations, which dominate DNN workloads. However, electronic circuitry is still necessary for performing nonlinear operations, control tasks, and data storage. Moreover, each photonic operation results in some power loss in the optical signal. As the number of consecutive photonic operations increases, the required input power grows exponentially, fundamentally limiting the number of operations that can be performed consecutively, even during linear operations. This limitation necessitates the storage of intermediate data, which is not feasible in optical form alone. Consequently, conversions between digital and analog domains are required, along with the use of traditional memory units like static random access memory (SRAM) and dynamic random access memory (DRAM). Frequent digital-to-analog (D-to-A) and analogto-digital (A-to-D) conversions, along with electrical-to-optical (E-to-O) and opticalto-electrical (O-to-E) conversions, combined with electronic arithmetic and memory operations, can create bottlenecks and significantly degrade the system's energy efficiency.

- 2. **Limited numeric precision in photonics:** In the analog domain, data are encoded in physical properties such as amplitude or phase, unlike the multiple bits used in the digital domain. This restricts analog operations to using only fixed-point (FXP) arithmetic, which offers a much lower dynamic range than floating-point (FP) arithmetic

for the same bit-width. Besides the absence of FP arithmetic, analog FXP operations present unique precision challenges in photonic tensor cores. The achievable precision in photonic hardware is limited by the signal-to-noise ratio (SNR) during analog operations and the bit precision of the digital-to-analog converters (DACs) and analog-to-digital converters (ADCs). Photonics suffers from multiple noise sources and non-idealities, including process variations, device noise, and environmental factors. Achieving high SNR is challenging because it requires exponentially increasing the input power with increasing bit-width to suppress noise. Moreover, the energy consumption of DACs and ADCs increases exponentially with their bit precision, making high-precision data converters impractical and limiting the input and output precision in analog operations. These limitations in numeric precision can cause significant accuracy loss in photonic hardware, even in DNN inference, especially in large state-of-the-art DNNs tackling complex problems.

#### 1.2 Thesis Contribution

The abovementioned challenges in photonic computing have limited its applicability to only very small DNNs and outdated tasks. While prior research has laid the groundwork for photonic AI hardware and shown promising results, there is a lack of detailed analysis to understand the technology's realistic potential and a clear roadmap for developing a hybrid electro-photonic accelerator capable of deploying state-of-the-art DNNs. Furthermore, the limited precision of photonic hardware has often been overlooked, as high precision was not required for the simple workloads evaluated in earlier studies. However, state-of-the-art DNNs demand higher precision to maintain accuracy, even for inference tasks. DNN training, in particular, has remained a distant goal for photonics, with efforts confined to a few studies focused on simple tasks and small models.

This thesis explores the opportunities and challenges of photonic computing for deep

learning acceleration with a pragmatic approach, to offer solutions to the abovementioned challenges. It is divided into three parts as follows: